DMA controller (DMA) RM0090

326/1731 DocID018909 Rev 11

If the DMEIFx or the FEIFx flag is set due to an overrun or underrun condition, the faulty

stream is not automatically disabled and it is up to the software to disable or not the stream

by resetting the EN bit in the DMA_SxCR register. This is because there is no data loss

when this kind of errors occur.

When the stream's error interrupt flag (TEIF, FEIF, DMEIF) in the DMA_LISR or DMA_HISR

register is set, an interrupt is generated if the corresponding interrupt enable bit (TEIE,

FEIE, DMIE) in the DMA_SxCR or DMA_SxFCR register is set.

Note: When a FIFO overrun or underrun condition occurs, the data are not lost because the

peripheral request is not acknowledged by the stream until the overrun or underrun

condition is cleared. If this acknowledge takes too much time, the peripheral itself may

detect an overrun or underrun condition of its internal buffer and data might be lost.

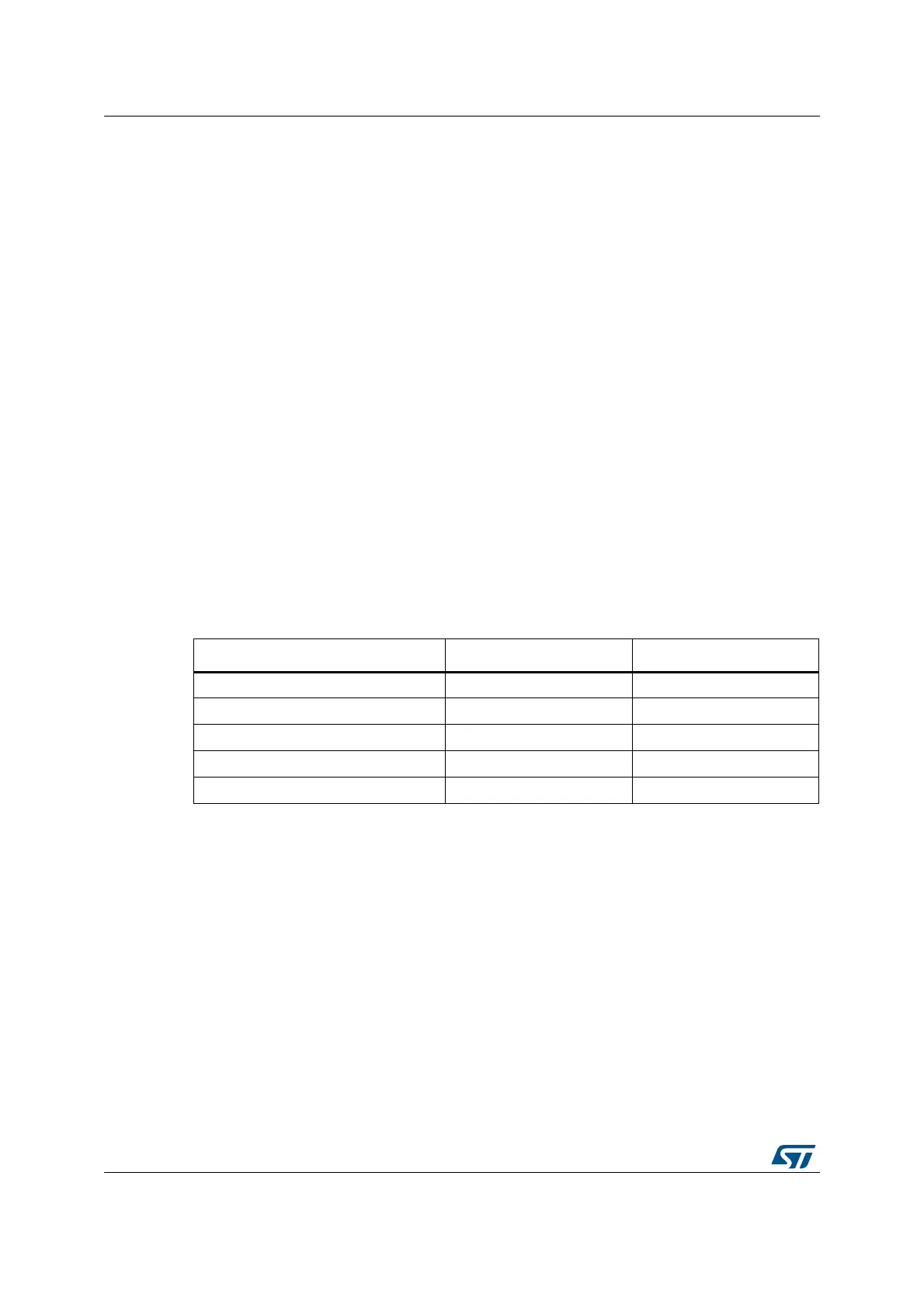

10.4 DMA interrupts

For each DMA stream, an interrupt can be produced on the following events:

• Half-transfer reached

• Transfer complete

• Transfer error

• Fifo error (overrun, underrun or FIFO level error)

• Direct mode error

Separate interrupt enable control bits are available for flexibility as shown in Table 50.

Note: Before setting an Enable control bit to ‘1’, the corresponding event flag should be cleared,

otherwise an interrupt is immediately generated.

Table 50. DMA interrupt requests

Interrupt event Event flag Enable control bit

Half-transfer HTIF HTIE

Transfer complete TCIF TCIE

Transfer error TEIF TEIE

FIFO overrun/underrun FEIF FEIE

Direct mode error DMEIF DMEIE

Loading...

Loading...