DocID018909 Rev 11 593/1731

RM0090 General-purpose timers (TIM2 to TIM5)

640

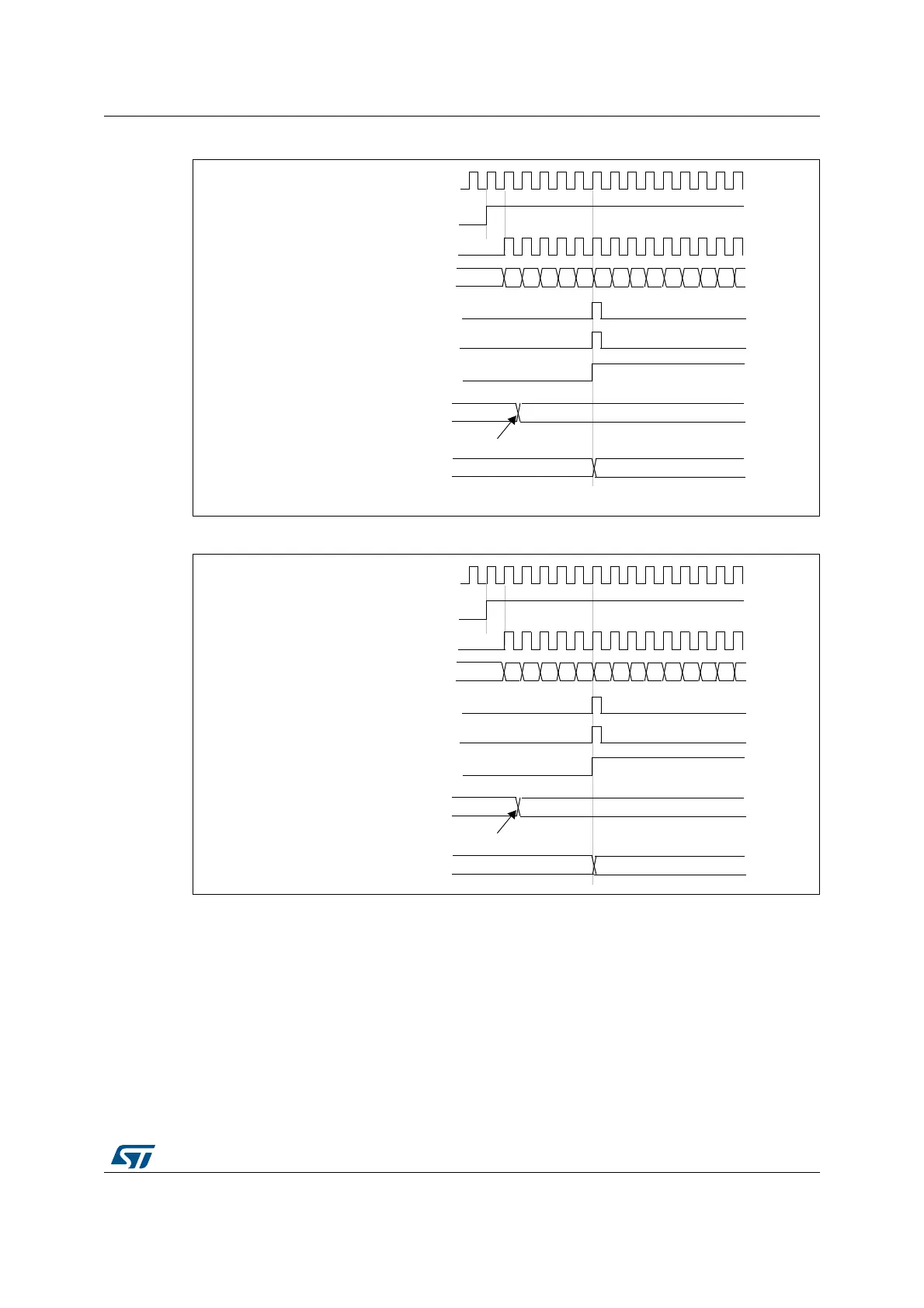

Figure 152. Counter timing diagram, Update event with ARPE=1 (counter underflow)

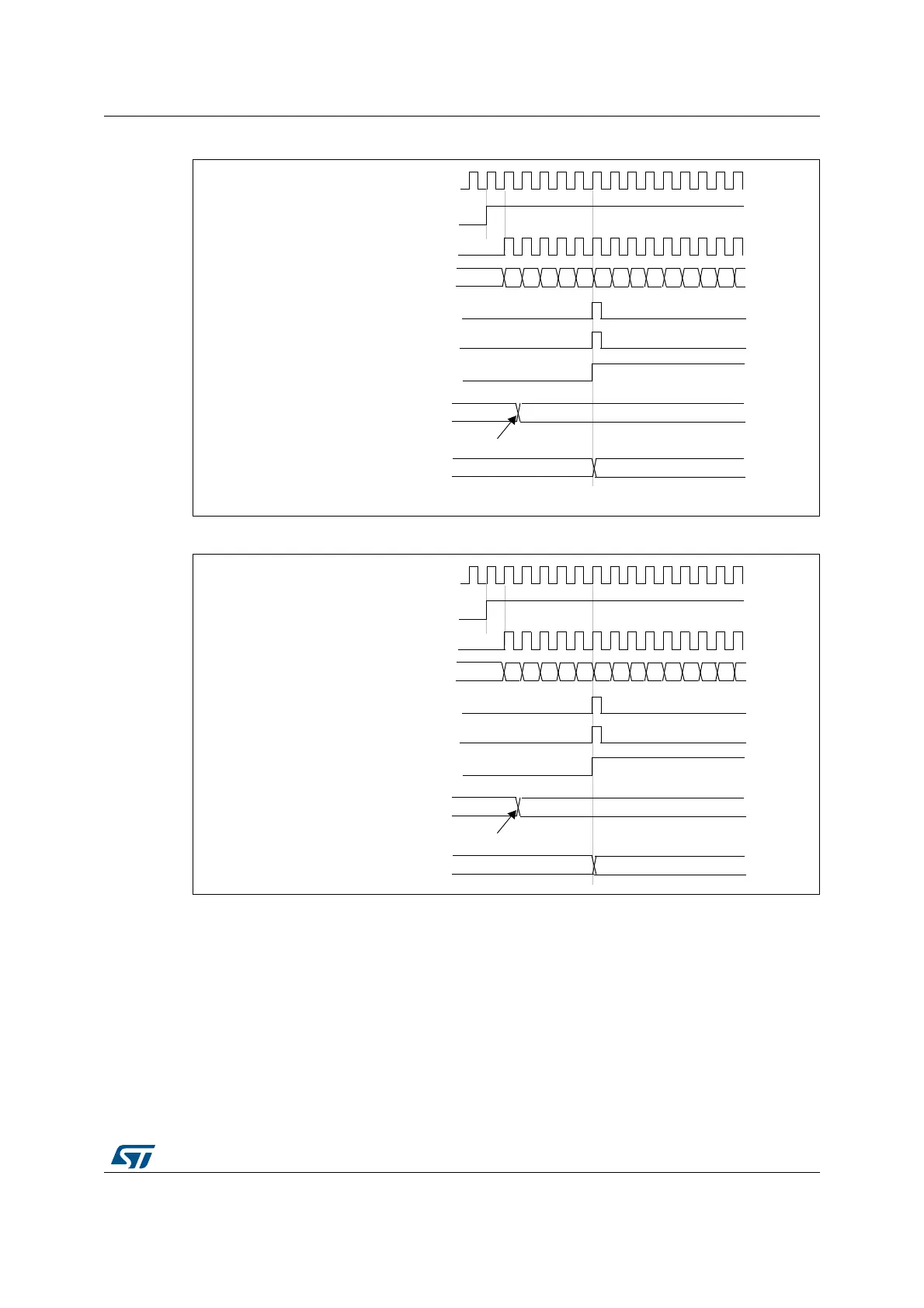

Figure 153. Counter timing diagram, Update event with ARPE=1 (counter overflow)

18.3.3 Clock selection

The counter clock can be provided by the following clock sources:

• Internal clock (CK_INT)

• External clock mode1: external input pin (TIx)

• External clock mode2: external trigger input (ETR) available on TIM2, TIM3 and TIM4

only.

• Internal trigger inputs (ITRx): using one timer as prescaler for another timer, for

example, you can configure Timer to act as a prescaler for Timer 2. Refer to : Using

one timer as prescaler for another timer on page 613 for more details.

00

CNT_EN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

Counter underflow

Update event (UEV)

01 02 03 04 05 06 0705 04 03 02 0106

Auto-reload preload register

FD 36

Write a new value in TIMx_ARR

Auto-reload active register

FD 36

CK_INT

36

CNT_EN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

Counter overflow

Update event (UEV)

35 34 33 32 31 30 2FF8 F9 FA FB FCF7

Auto-reload preload register

FD 36

Write a new value in TIMx_ARR

Auto-reload active register

FD 36

CK_INT

Loading...

Loading...