DocID018909 Rev 11 1685/1731

RM0090 Debug support (DBG)

1701

38.10 Core debug

Core debug is accessed through the core debug registers. Debug access to these registers

is by means of the Advanced High-performance Bus (AHB-AP) port. The processor can

access these registers directly over the internal Private Peripheral Bus (PPB).

It consists of 4 registers:

Note: Important: these registers are not reset by a system reset. They are only reset by a power-

on reset.

Refer to the Cortex

®

-M4 with FPU r0p1 TRM for further details.

To Halt on reset, it is necessary to:

• enable the bit0 (VC_CORRESET) of the Debug and Exception Monitor Control

Register

• enable the bit0 (C_DEBUGEN) of the Debug Halting Control and Status Register.

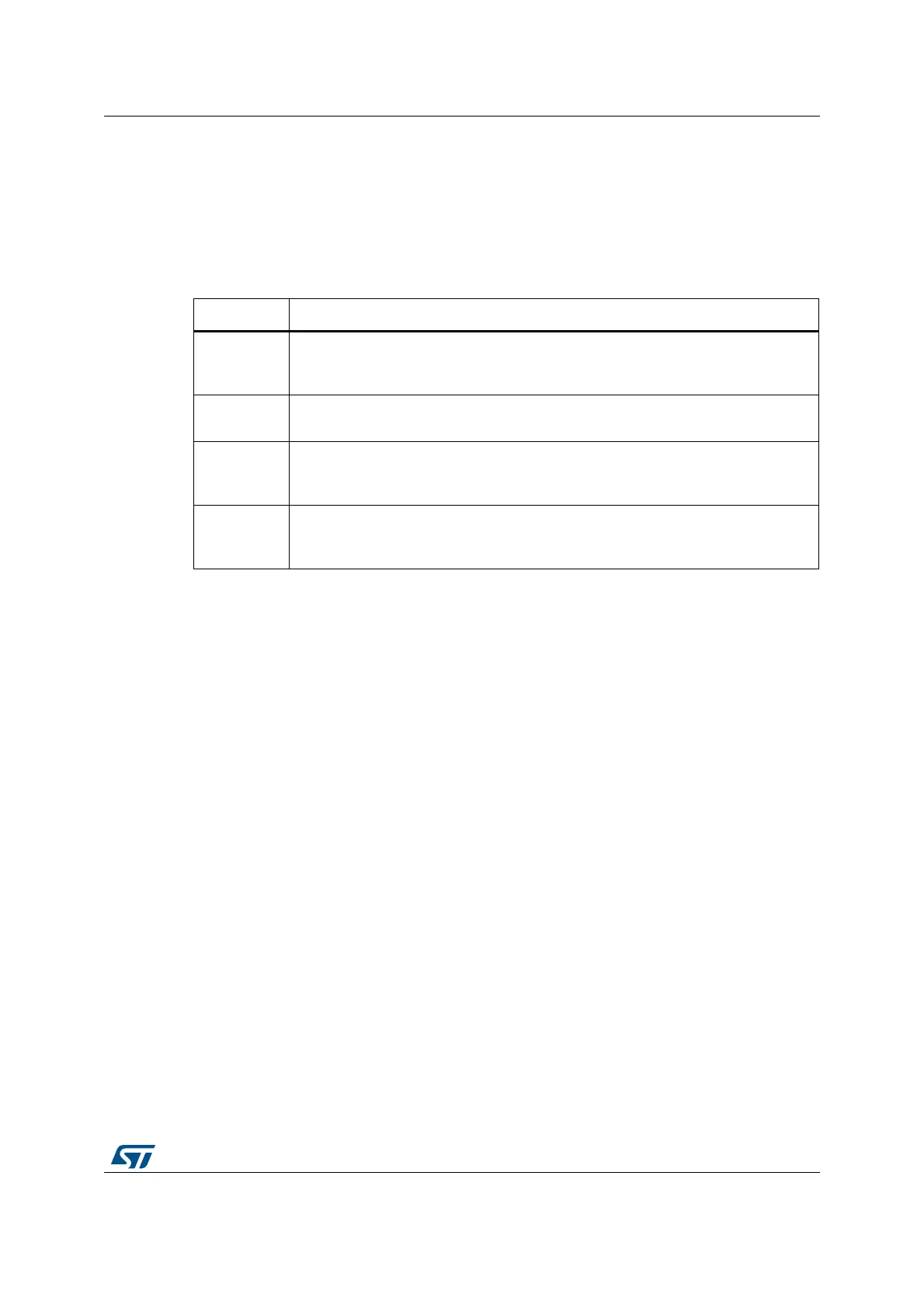

Table 302. Core debug registers

Register Description

DHCSR

The 32-bit Debug Halting Control and Status Register

This provides status information about the state of the processor enable core debug

halt and step the processor

DCRSR

The 17-bit Debug Core Register Selector Register:

This selects the processor register to transfer data to or from.

DCRDR

The 32-bit Debug Core Register Data Register:

This holds data for reading and writing registers to and from the processor selected

by the DCRSR (Selector) register.

DEMCR

The 32-bit Debug Exception and Monitor Control Register:

This provides Vector Catching and Debug Monitor Control. This register contains a

bit named TRCENA which enable the use of a TRACE.

Loading...

Loading...