DocID018909 Rev 11 863/1731

RM0090 Inter-integrated circuit (I

2

C) interface

864

27.6.10 I

2

C FLTR register (I2C_FLTR)

Address offset: 0x24

Reset value: 0x0000

The I2C_FLTR is available on STM32F42xxx and STM32F43xxx only.

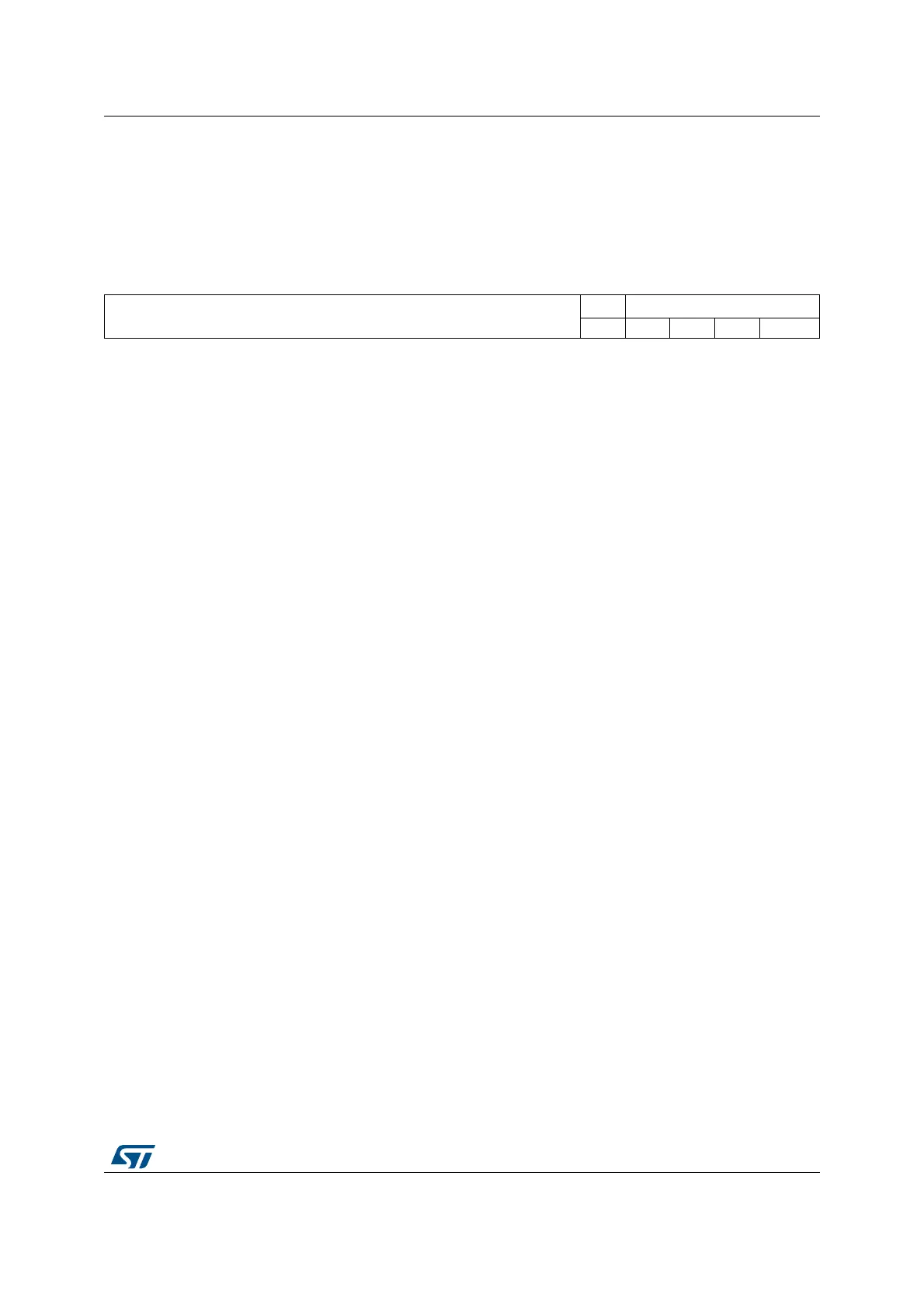

151413121110987 654321 0

Reserved

ANOFF

DNF[3:0]

rw rw rw rw rw

Bits 15:5 Reserved, must be kept at reset value

Bit 4 ANOFF: Analog noise filter OFF

0: Analog noise filter enable

1: Analog noise filter disable

Note: ANOFF must be configured only when the I2C is disabled (PE = 0).

Bits 3:0 DNF[3:0]: Digital noise filter

These bits are used to configure the digital noise filter on SDA and SCL inputs. The digital filter

will suppress the spikes with a length of up to DNF[3:0] * TPCLK1.

0000: Digital noise filter disable

0001: Digital noise filter enabled and filtering capability up to 1* TPCLK1.

...

1111: Digital noise filter enabled and filtering capability up to 15* TPCLK1.

Note: DNF[3:0] must be configured only when the I2C is disabled (PE = 0). If the analog filter

is also enabled, the digital filter is added to the analog filter.

Loading...

Loading...