Z8 Microcontrollers

Instruction Descriptions and Formats ZiLOG

12-32 UM001601-0803

INC

INCREMENT

Inc

Increment

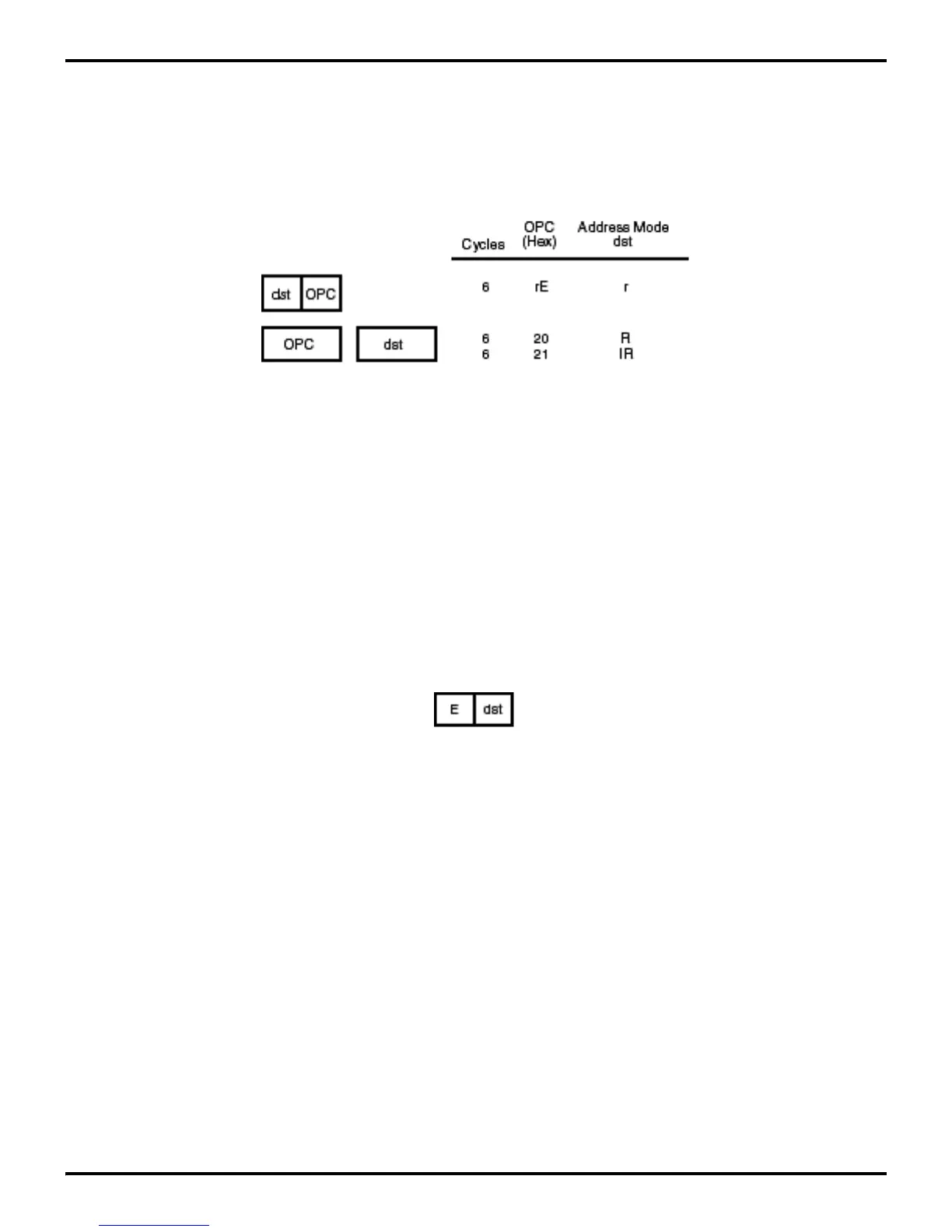

Instruction Format:

Operation:

dst <— dst + 1

The contents of the destination operand are incremented by one.

Note:

Address modes R or IR can be used to specify a 4-bit Working Register. In this format, the destination Working

Register operand is specified by adding 1110B (EH) to the high nibble of the operand. For example, if Working

Register R12 (CH) is the destination operand, then ECH will be used as the destination operand in the Op Code.

Example:

If Working Register R10 contains 2AH, the statement:

INC R10

Op Code: AE

leaves the value 2BH in Working Register R10. The Z, V, and S Flags are cleared.

Example:

If Register B3H contains CBH, the statement:

INC B3H

Op Code: 20 B3

leaves the value CCH in Register CBH. The S Flag is set, and the Z and V Flags are cleared.

Example:

If Register B3H contains CBH and Register BCH contains FFH, the statement:

INC @B3H

Op Code: 21 B3

leaves the value 00H in Register CBH. The Z Flag is set, and the V and S Flags are cleared.

Flags: C: Unaffected

Z: Set if the result is zero; cleared otherwise.

S: Set if the result of bit 7 is set (negative); cleared otherwise.

V: Set if arithmetic overflow occurs; cleared otherwise.

D: Unaffected

H: Unaffected

Loading...

Loading...