Interrupt Sources

www.ti.com

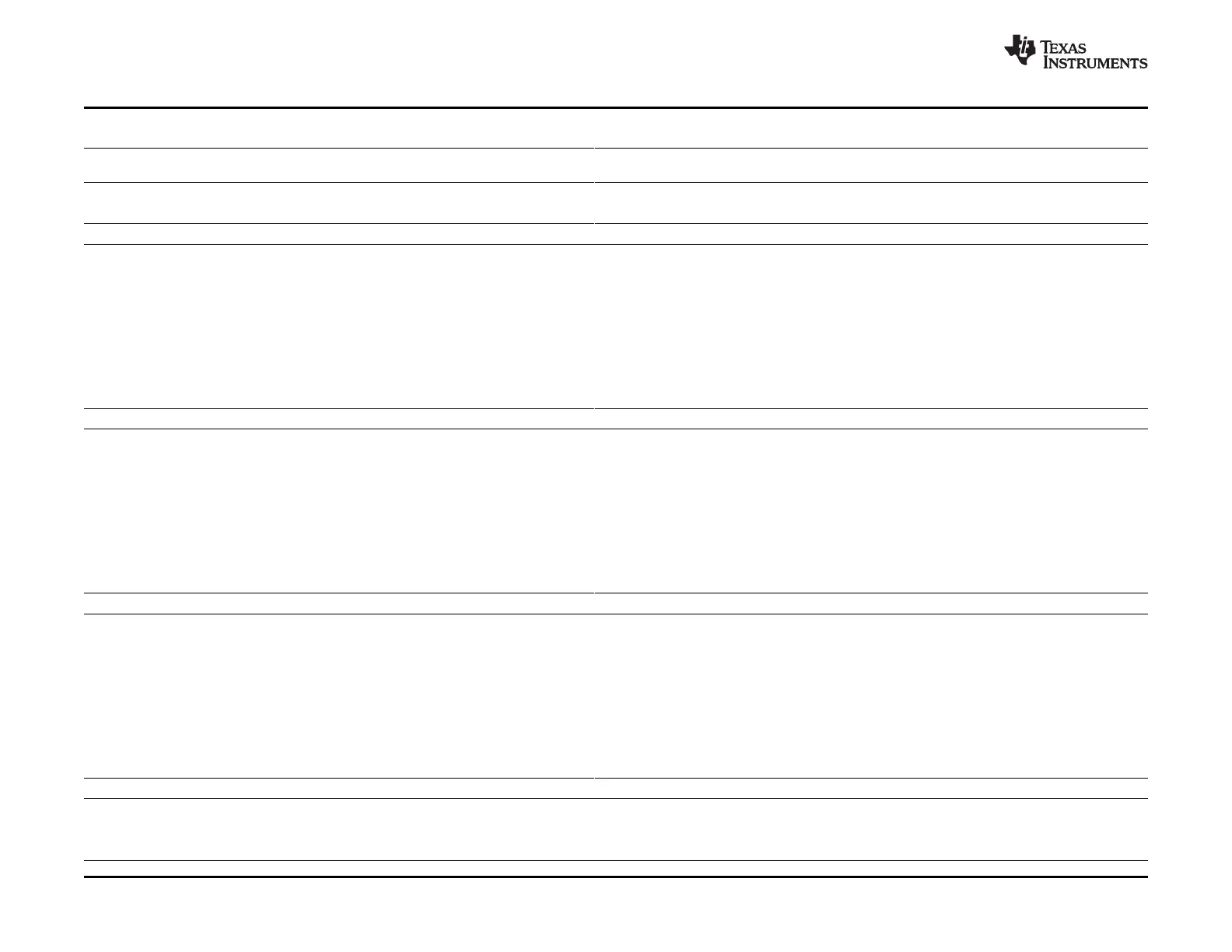

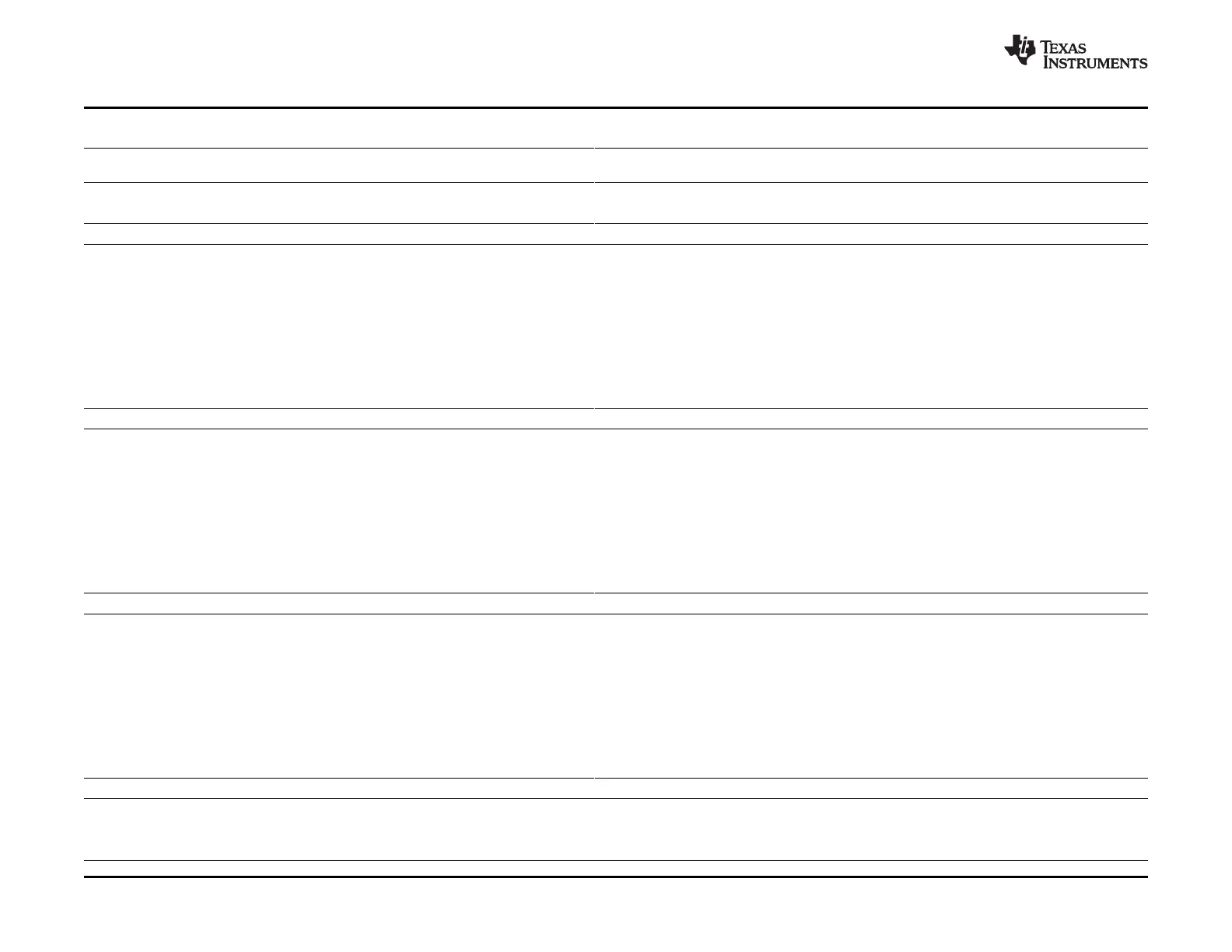

Table 6-5. PIE Vector Table (continued)

PIE Group

Name VECTOR ID

(1)

Address

(2)

Size (x16) Description

(3)

CPU Priority Priority

INT3.7 54 0x0000 0D6C 2 Reserved 7 7

INT3.8 55 0x0000 0D6E 2 Reserved 7 8 (lowest)

PIE Group 4 Vectors - MUXed into CPU INT4

INT4.1 56 0x0000 0D70 2 ECAP1_INT (ECAP1) 8 1 (highest)

INT4.2 57 0x0000 0D72 2 ECAP2_INT (ECAP2) 8 2

INT4.3 58 0x0000 0D74 2 ECAP3_INT (ECAP3) 8 3

INT4.4 59 0x0000 0D76 2 ECAP4_INT (ECAP4) 8 4

INT4.5 60 0x0000 0D78 2 ECAP5_INT (ECAP5) 8 5

INT4.6 61 0x0000 0D7A 2 ECAP6_INT (ECAP6) 8 6

INT4.7 62 0x0000 0D7C 2 Reserved 8 7

INT4.8 63 0x0000 0D7E 2 Reserved 8 8 (lowest)

PIE Group 5 Vectors - MUXed into CPU INT5

INT5.1 64 0x0000 0D80 2 EQEP1_INT (EQEP1) 9 1 (highest)

INT5.2 65 0x0000 0D82 2 EQEP2_INT (EQEP2) 9 2

INT5.3 66 0x0000 0D84 2 Reserved 9 3

INT5.4 67 0x0000 0D86 2 Reserved 9 4

INT5.5 68 0x0000 0D88 2 Reserved 9 5

INT5.6 69 0x0000 0D8A 2 Reserved 9 6

INT5.7 70 0x0000 0D8C 2 Reserved 9 7

INT5.8 71 0x0000 0D8E 2 Reserved 9 8 (lowest)

PIE Group 6 Vectors - MUXed into CPU INT6

INT6.1 72 0x0000 0D90 2 SPIRXINTA (SPI-A) 10 1 (highest)

INT6.2 73 0x0000 0D92 2 SPITXINTA (SPI-A) 10 2

INT6.3 74 0x0000 0D94 2 MRINTB (McBSP-B) 10 3

INT6.4 75 0x0000 0D96 2 MXINTB (McBSP-B)(SPI-B) 10 4

INT6.5 76 0x0000 0D98 2 MRINTA (McBSP-A) 10 5

INT6.6 77 0x0000 0D9A 2 MXINTA (McBSP-A) 10 6

INT6.7 78 0x0000 0D9C 2 Reserved 10 7

INT6.8 79 0x0000 0D9E 2 Reserved 10 8 (lowest)

PIE Group 7 Vectors - MUXed into CPU INT7

INT7.1 80 0x0000 0DA0 2 DINTCH1 DMA Channel 1 11 1 (highest)

INT7.2 81 0x0000 0DA2 2 DINTCH2 DMA Channel 2 11 2

INT7.3 82 0x0000 0DA4 2 DINTCH3 DMA Channel 3 11 3

136 Peripheral Interrupt Expansion (PIE) SPRUFB0C – September 2007 – Revised May 2009

Submit Documentation Feedback

Loading...

Loading...