MPC5200B Users Guide, Rev. 1

3-8 Freescale Semiconductor

MPC5200B Memory Map

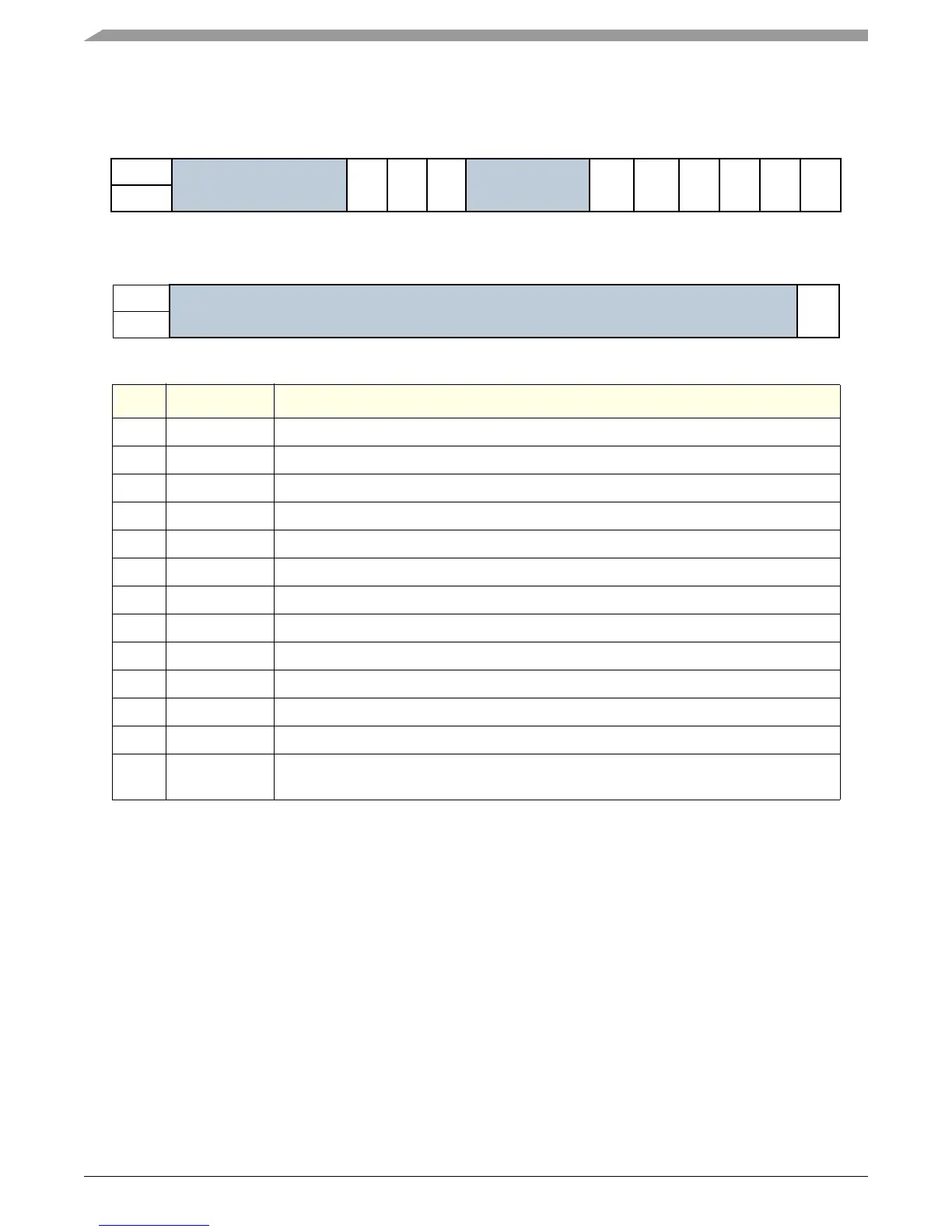

3.3.3.4 IPBI Control Register and Wait State Enable —MBAR+0x0054

The IPBI Control Register consists of the Enables for the Base Addresses set in Memory Map Space

msb 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R Reserved CS7

Ena

CS6

Ena

Boot

Ena

Reserved CS5

Ena

CS4

Ena

CS3

Ena

CS2

Ena

CS1

Ena

CS0

Ena

W

RESET 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Reserved WSE

W

RESET0000000000000001

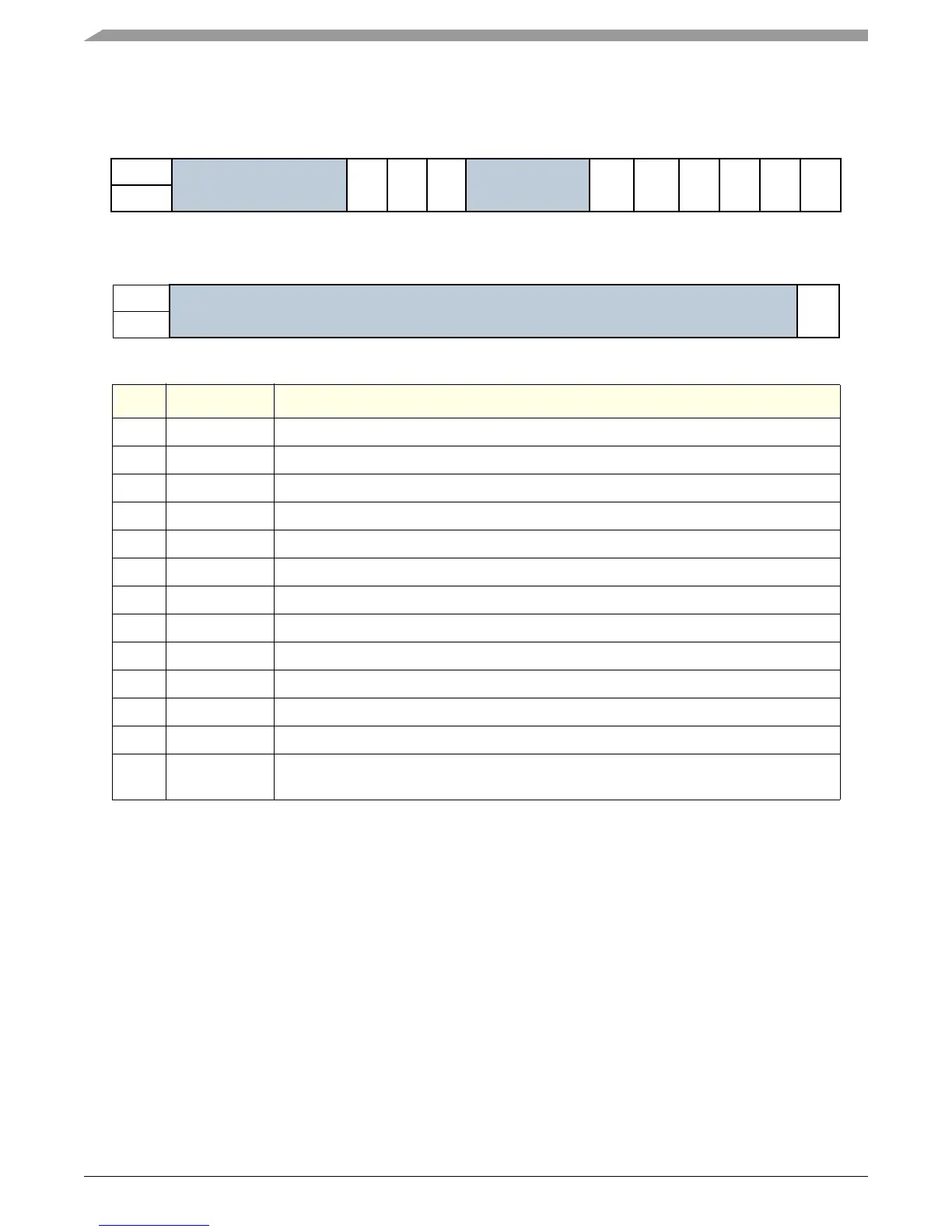

Bits Name Description

0:3 Reserved These bits are reserved.

4 CS7 Ena Chip Select 7 Enable

5 CS6 Ena Chip Select 6 Enable

6 Boot Ena Boot Enable

7:9 Reserved These bits are reserved.

10 CS5 Ena Chip Select 5 Enable

11 CS4 Ena Chip Select 4 Enable

12 CS3 Ena Chip Select 3 Enable

13 CS2 Ena Chip Select 2 Enable

14 CS1 Ena Chip Select 1 Enable

15 CS0 Ena Chip Select 0 Enable

16:30 Reserved These bits are reserved.

31 WSE Wait State Enable bit. This bit should always be enabled when running an IP bus frequency

of >66MHz.

Loading...

Loading...