MPC5200B Users Guide, Rev. 1

14-4 Freescale Semiconductor

I/O Signal Overview

14.3.1 Detailed Signal Descriptions

14.3.1.1 MII Ethernet MAC-PHY Interface

This section gives a detailed description of the Media-Independent Interface (MII). An overview of the MII is presented followed by a

description of the MII signals. Two different types of MII frames are described. A brief MII management function overview is given.

The MII interface has 18 signals. Tx and Rx functions require 7 signals each:

• 4 data signals

• 1 delimiter

•1 error

• 1 clock

Media status is indicated by 2 signals:

• 1 signal indicates a carrier is present.

• 1 signal indicates a collision occurred.

Management interface is provided by 2 signals.

MII signals are described below.

Tx_CLK . . . . . . . . . . . . A continuous clock that provides a timing reference for Tx_EN, TxD, and Tx_ER. The frequency of Tx_CLK

is 25% of the transmit data rate, ± 100 ppm. Duty cycle shall be 35%-65% inclusive.

Rx_CLK. . . . . . . . . . . . A continuous clock that provides a timing reference for Rx_DV, RxD, and Rx_ER. The frequency of Rx_CLK

is 25% of the receive data rate, with a duty cycle between 35% and 65%.

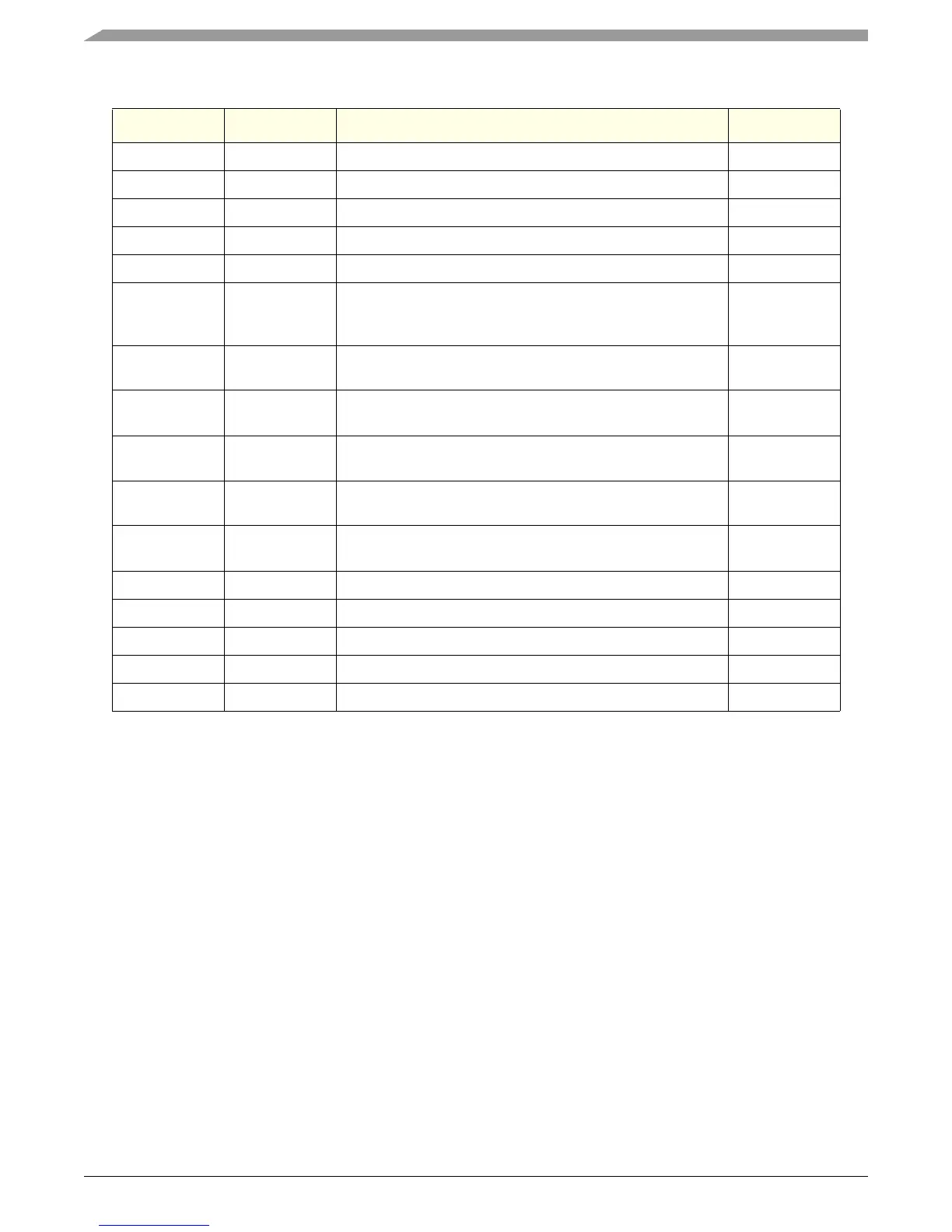

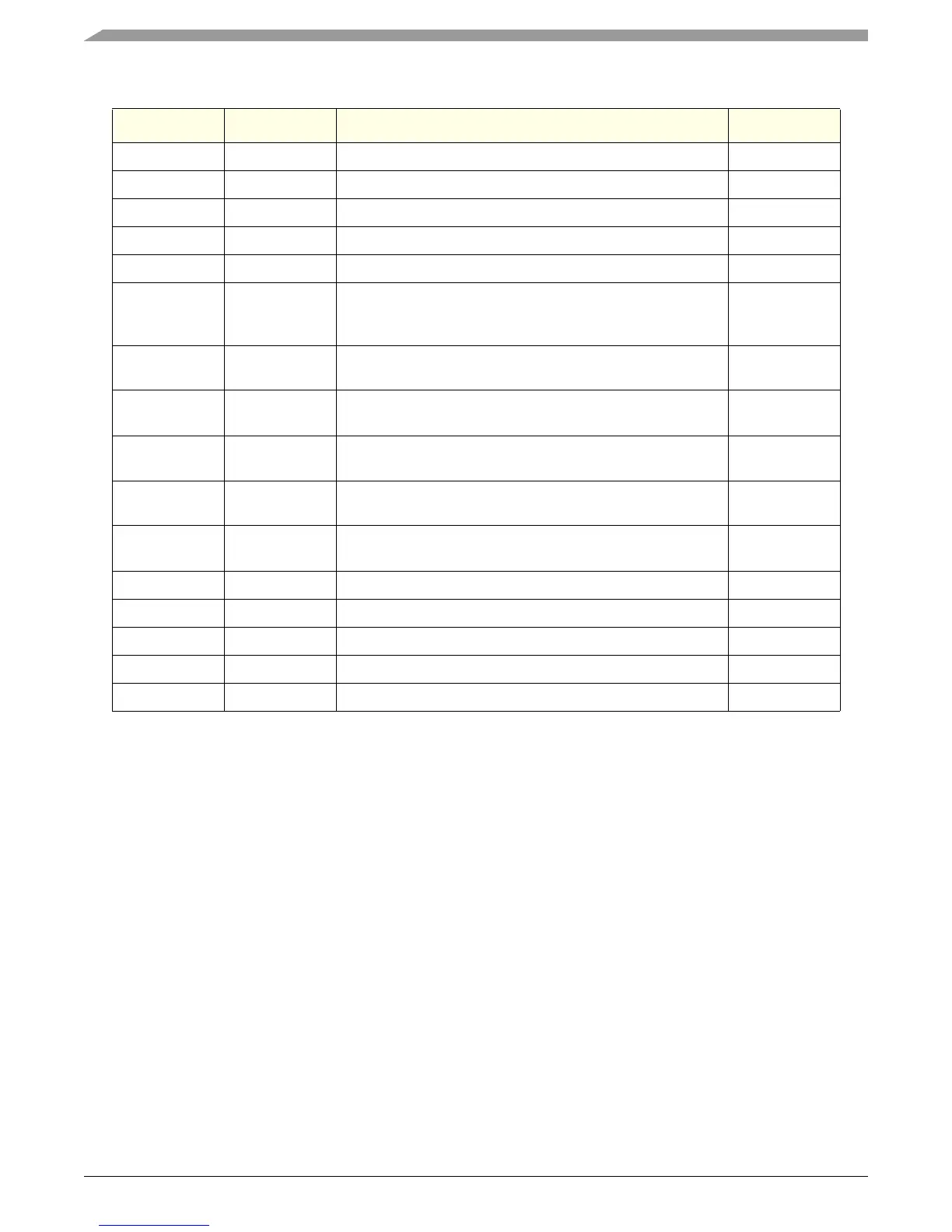

tdata[1] ETH2 MII—transmit data bit 1 output

tdata[2] ETH3 MII—transmit data bit 2 output

tdata[3] ETH4 MII—transmit data bit 3 output

tx_er ETH5 MII—transmit error output 0

mdc ETH6 MII—management clock output 0

mdi

mdo

md_en

ETH7 MII—management data bidirect Hi-Z (input)

rx_dv ETH8 MII—Rx data valid input

7-wire—rena input

rx_clk ETH9 MII—Rx clock input

7-wire—Rx clock input

col ETH10 MII—collision input

10 Mbps 7-wire—collision input

tx_clk ETH11 MII—transmit clock input

7-wire—transmit clock input

rdata[0] ETH12 MII—Rx data bit 0 input

7-wire—Rx data input

rdata[1] ETH13 MII—Rx data bit 1 input

rdata[2] ETH14 MII—Rx data bit 2 input

rdata[3 ] ETH15 MII—Rx data bit 3 input

rx_er ETH16 MII—Rx error input

crs ETH17 MII—carrier sense input

Table 14-1. Signal Properties (continued)

Signal Name Chip Pin Function Reset State

Loading...

Loading...