MPC5200B Users Guide, Rev. 1

7-4 Freescale Semiconductor

Interrupt Controller

7.2.2 Interface Description

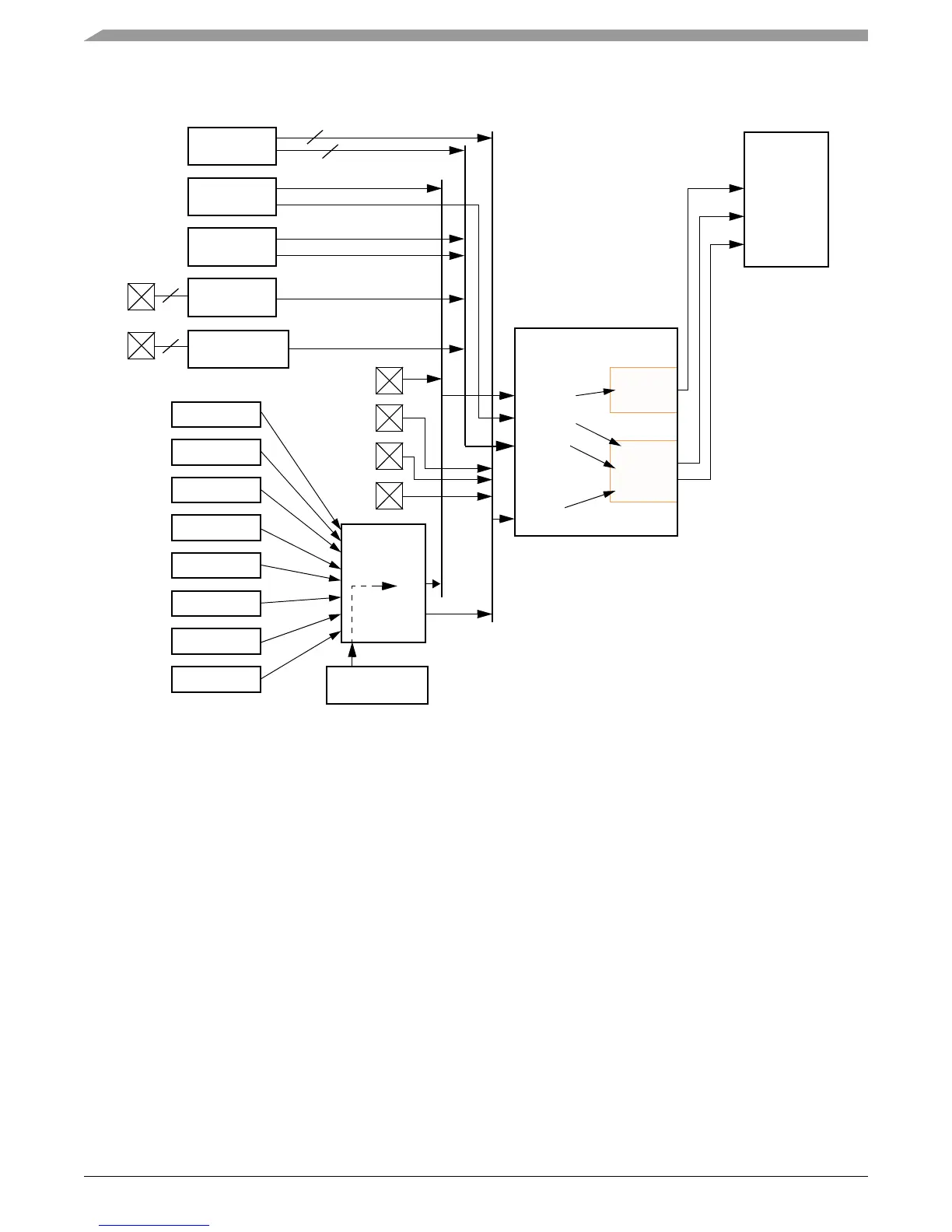

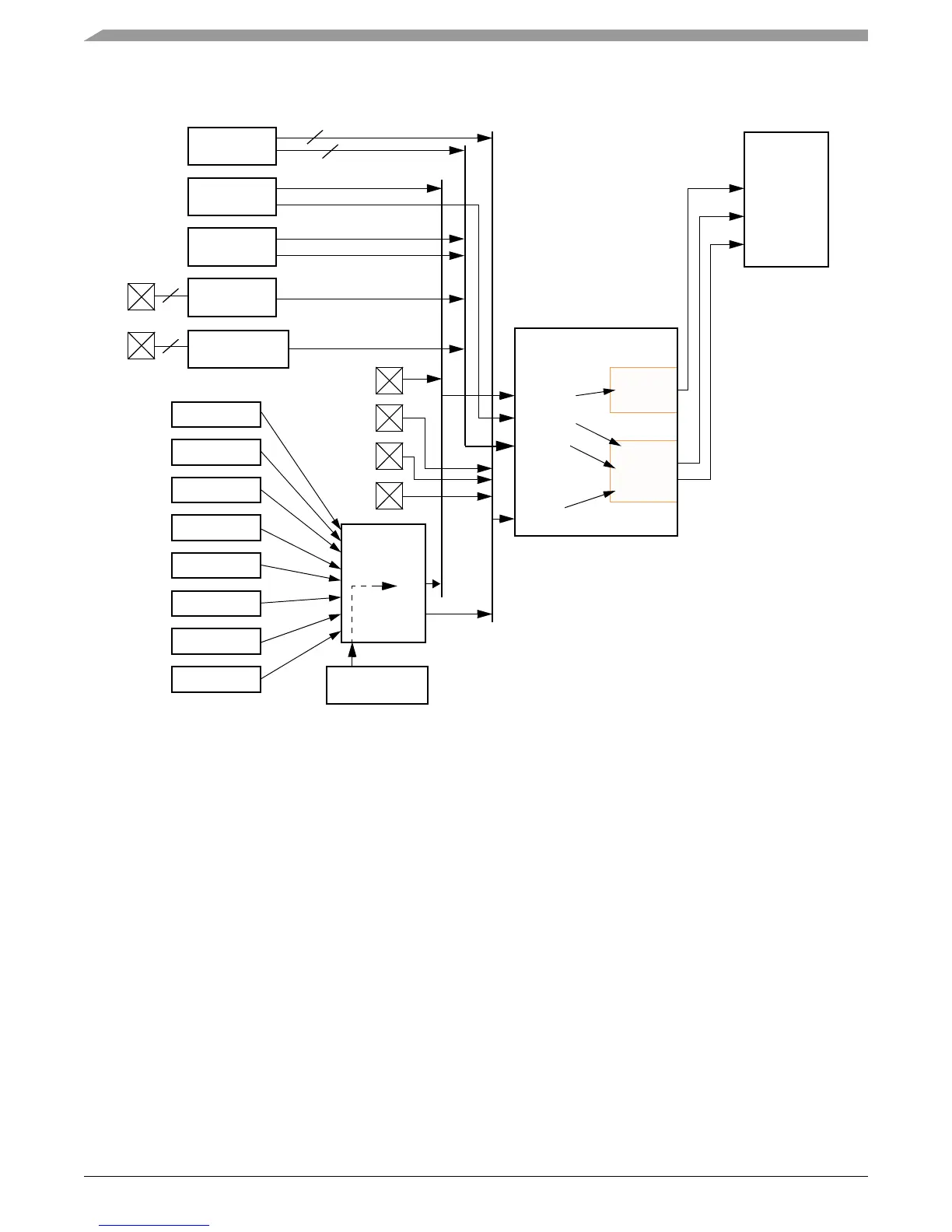

Figure 7-2. Interrupt Controller Routing Scheme

7.2.3 Programming Note

Under specific conditions, the Interrupt Controller may not support nested interrupts. The Interrupt Controller may prevent the

assertion of a core_cint interrupt if a core_int or a core_smi is pending. Similarly, the Interrupt Controller may block a core_smi if

a core_int is pending. If the e300 core received the core_cint assertion during an core_int or core_smi assertion, it would preempt the current

interrupt service routine and process the Critical Interrupt Service routine immediately. Since the MPC5200B Interrupt Controller postpones

the core_cint assertion until after a current core_int or core_smi is finished, there can be a delay before the 603e receives and services Critical

Interrupt Sources.

The interrupt Controller always supports nested interrupt if the Critical Interrupt sources come from IRQ0, Slice TImer 0 or the wakeup logic.

There is a difference when the critical source comes from HI_int (Peripheral Interrupt Group). As shown in Figure 7-2, each Peripheral

Interrupt can assert a HI_int or LO_int condition. But only one Peripheral Interrupt can be active at the time, so the Interrupt Controller has

not the ability to simultaneously assert both HI_int and LO_int. Therefore, the peripheral 2 which generated by default a core_int (LO_int)

interrupt will prevent a BestComm Interrupt to generate a core_cint (HI_int) interrupt.

In addition, a Peripheral Interrupt directed to a core_cint can be prevented by a pending core_smi interrupt. Each Peripheral Interrupt (LO_int)

can be programmed to cause a core_smi by setting the Main4_pri msb. Once again, the Interrupt Controller does not has the ability to

simultaneously generate the HI_int and LO_int. Then, a Peripheral Interrupt, which generates a core_smi, prevents any Peripheral Interrupts

to assert a core_cint.

Similarly, the Interrupt Controller can activate only one Main Interrupt source at the time. Main4 source is the collection of all LO_int

Peripheral Interrupts. The Main4_pri can be programmed in order to generate a core_smi or a core_int. As result, a Peripheral Interrupt that

causes a core_int will prevent all other Main Interrupt sources to generate a core_smi. Although the Interrupt Controller does not exhibit the

4

4

Peripheral 1

Peripheral 2

Peripheral 3

Peripheral 4

Peripheral 5

Peripheral 6

Peripheral …

XLB Arbiter

HI

LO

BestComm

Controller

IRQ0

IRQ1

IRQ2

IRQ3

Encoder

Grouper

Encoder

cint_ded

smi_ded

int_ded

programmable inputs

Grouper

Encoder

Main Interrupt

Controller

e300 core

core_mcp

core_cint

core_smi

core_int

Timers

(IC, OC, PWM)

Slice

0

1Timers

Real Time

Clock

GPIO/WakeUp

GPIO/Std

NOTE:

1. Grouper and Encoder functions imply

programmability in software.

8

8

Loading...

Loading...