MPC5200B Users Guide, Rev. 1

12-4 Freescale Semiconductor

Host Controller Interface

Figure 12-4. Interrupt ED Structure

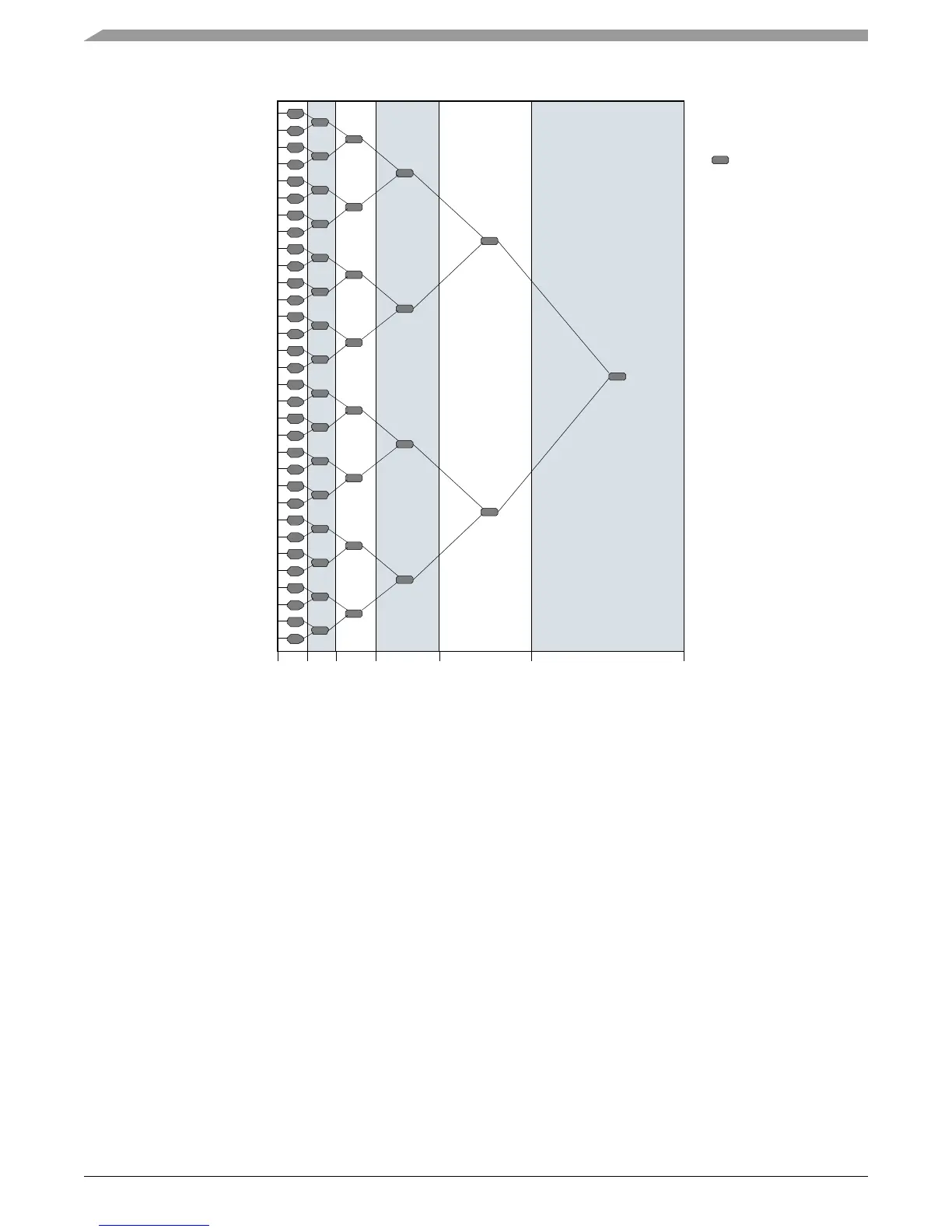

Figure 12-5 shows a sample interrupt endpoint schedule. The schedule shows:

• two endpoint descriptors at a 1ms poll interval

• two endpoint descriptors at a 2ms poll interval

• one endpoint descriptor at a 4ms poll interval

• two endpoint descriptors at an 8ms poll interval

• two endpoint descriptors at a 16ms poll interval

• two endpoint descriptors at a 32ms poll interval.

NOTE

Unused interrupt endpoint placeholders are bypassed and the link is connected to the next available

endpoint in the hierarchy.

0

17

8

1

2

3

4

5

6

7

9

10

11

12

13

14

15

16

24

20

28

18

26

22

30

25

21

29

19

27

23

31

32 16 8 4 2

1

Interrupt

Endpoint

Descriptor

Placeholder

Endpoint Poll Interval (ms)

Interrupt

Headpointers

Loading...

Loading...