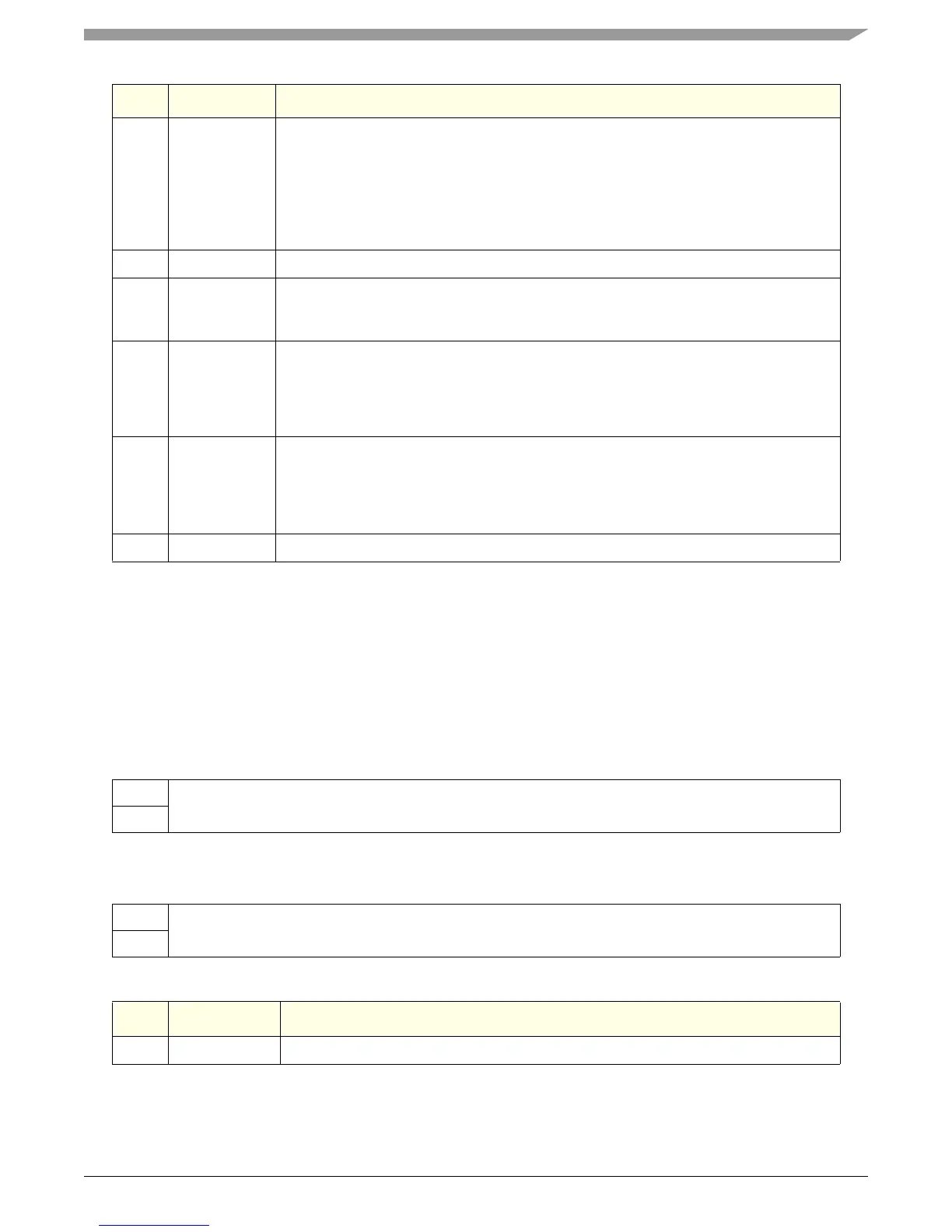

XLB Arbiter Registers—MBAR + 0x1F00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 16-5

NOTE

The PLDIS reset value is 1, which means the XLB Arbiter will prohibit transaction pipelining. In

most applications, transaction pipelining will provide a significant performance increase, and

therefore the customer should consider setting this bit to 0 to take advantage of this increase.

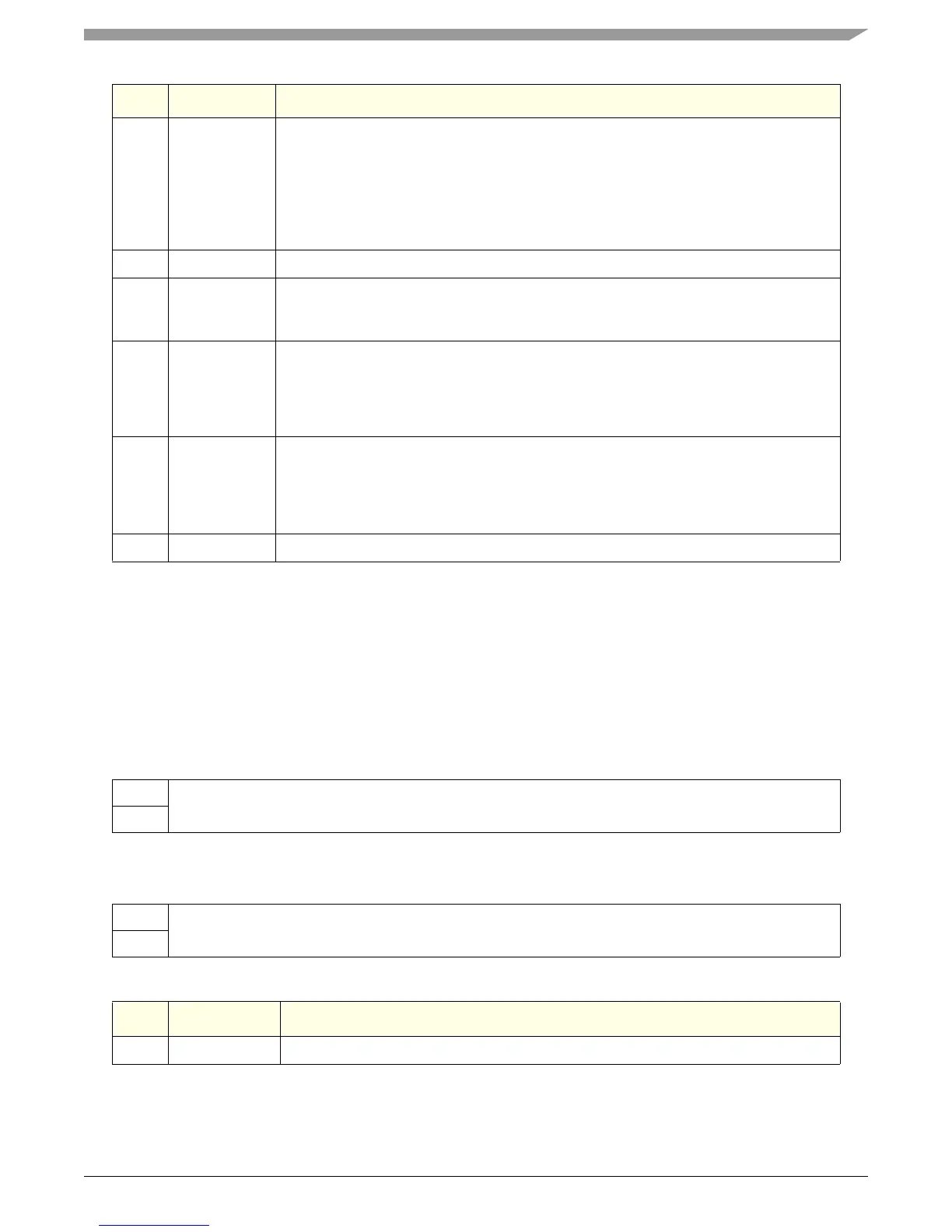

16.2.2 Arbiter Version Register (R)—MBAR + 0x1F44

The Arbiter Version Register contains the silicon version number for the arbiter hardware.

16.2.3 Arbiter Status Register (R/W)—MBAR + 0x1F48

The Arbiter Status Register indicates the state of watchdog functions. When a monitored condition occurs, the respective bit is set to 1. The

bit remains 1 until cleared by writing 1 into that bit position. Even if the causal condition is removed, the bit remains set until cleared.

25:26 PM[1:0] Parking Mode.

00 = No parking (default).

01 = Reserved.

10 = Park on most recently used master.

11 = Park on programmed master as specifed by the Select Parked Master bits 21:23

above.

27 — Reserved

28 BA Bus Activity Time-out Enable. If enabled, the arbiter will set the Bus Activity Time-out Status

bit (Arbiter Status Register, bit 29) when the Bus Activity Time-out is reached. Bus Activity

Time-out is derived from the Arbiter Bus Activity Time Out Count register.

29 DT Data Tenure Time-out Enable. If enabled, the arbiter will assert TEA when the Data Tenure

Time-out is reached. Data Tenure Time-out is derived from the Arbiter Data Tenure Time

Out Count Register. Also, the arbiter will set the Data Tenure Time-out Status bit (Arbiter

Status Register, bit 30). Setting this bit will also enable the Address Tenure Time-out. This

is required to ensure that a data time-out will not occur before an address acknowledge.

30 AT Address Tenure Time-out Enable. If enabled, the arbiter will assert AACK and TEA (if

required) when the Address Tenure Time-out is reached. Address Tenure Time-out is

derived from the Arbiter Address Tenure Time Out Count register. Also, the arbiter will set

the Address Tenure Time-out Status bit (Arbiter Status Register, bit 31). Address Tenure

Time-out is also enabled by the DT bit above.

31 — Reserved

Table 16-2. Arbiter Version Register

msb 012345678 9 1011121314 15

R Version ID[0:15]

W

RESET:0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R Version ID[16:31]

W

RESET:0 00000000 0 0 0 00 0 1

Bit Name Description

0:31 VER Hardware version ID. The current version number is 0x0001.

Bit Name Description

Loading...

Loading...