Architecture

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 1-5

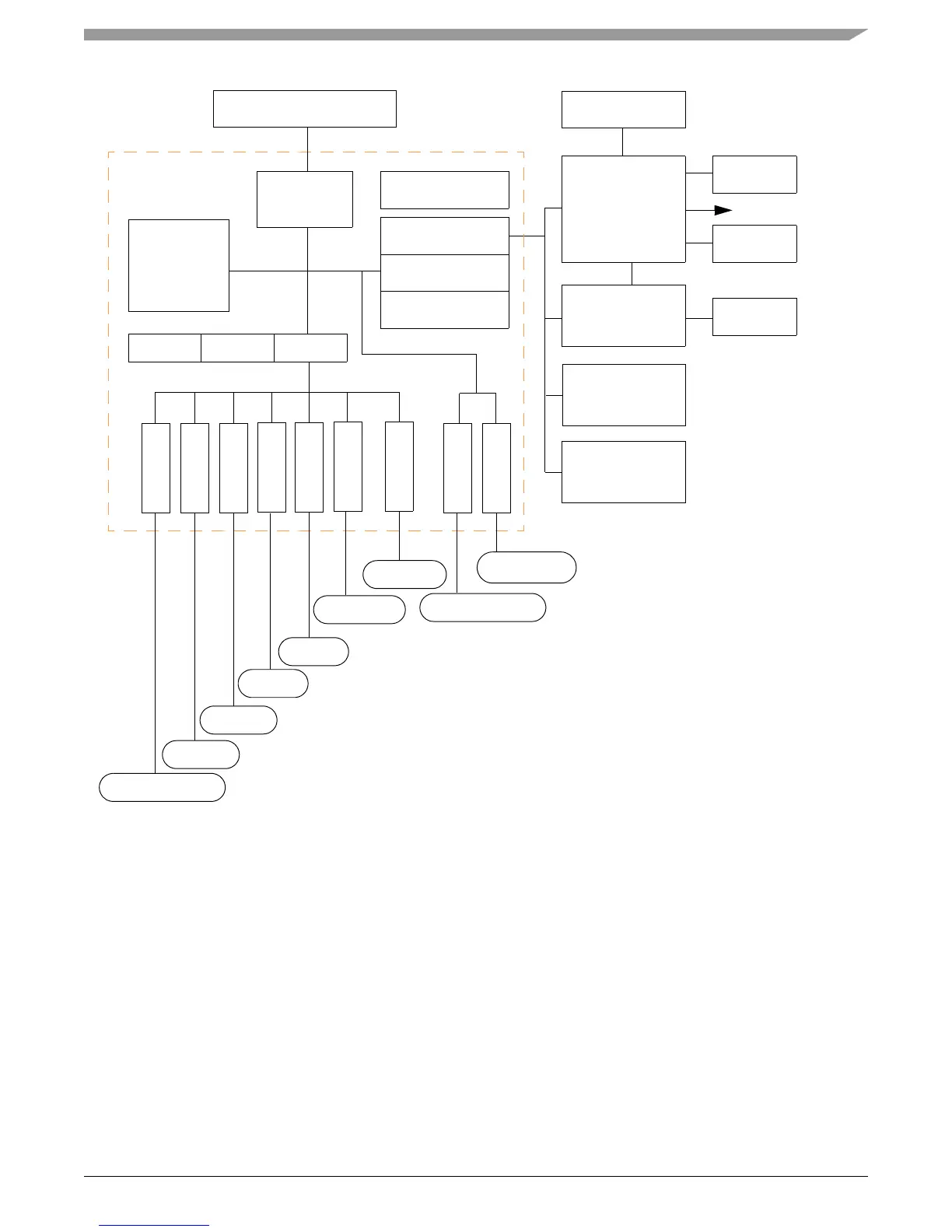

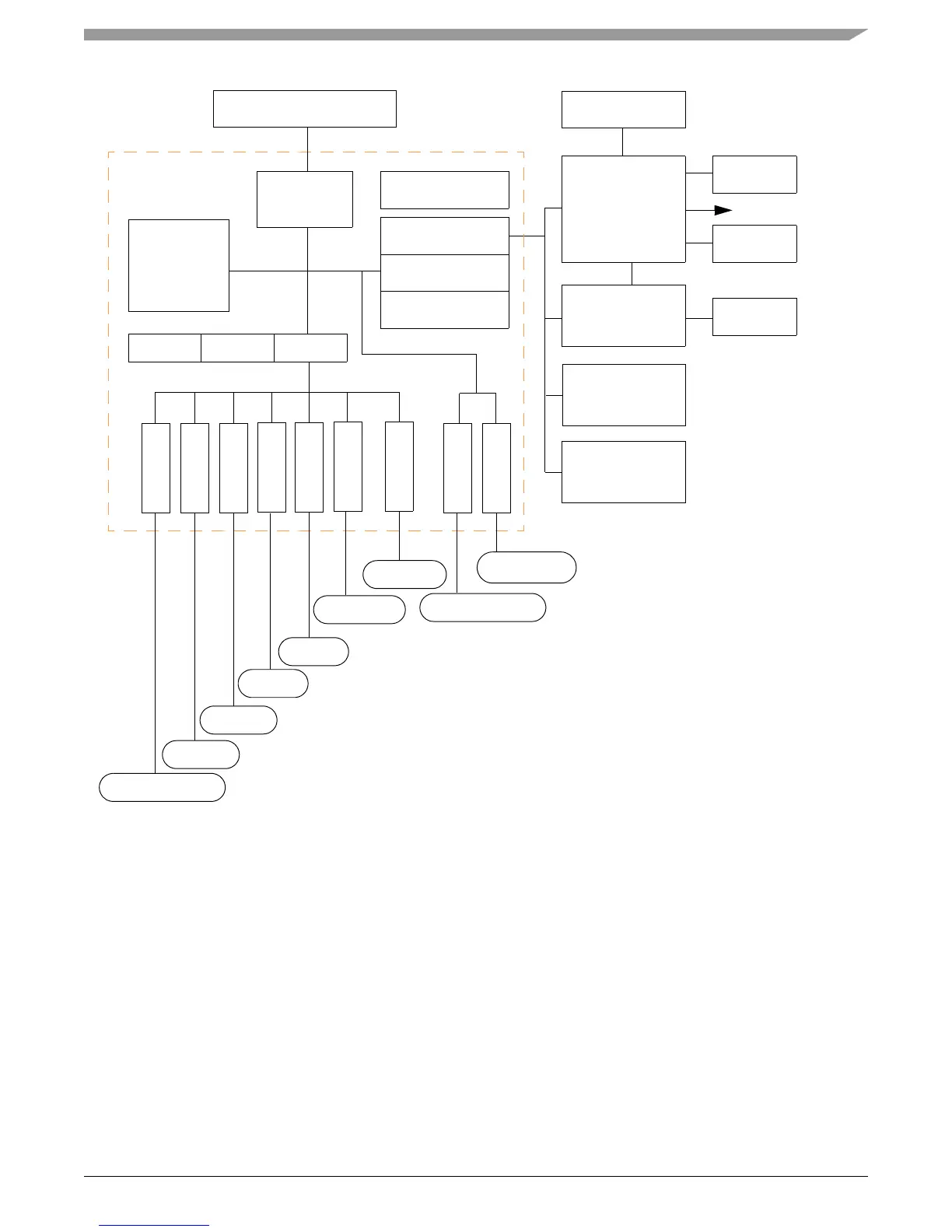

Figure 1-2. MPC5200B-Based System

1.2.1 Embedded e300 Core

The MPC5200B embedded e300 core is derived from Freescale’s (formerly Motorola) MPC603e family of Reduced Instruction Set Computer

(RISC) microprocessors. The e300 core is a high-performance, low-power implementation of the PowerPC superscalar architecture. The

MPC5200B e300 core contains:

• 16KBytes of instruction cache

• 16KBytes of data cache

Caches are 4-way set associative and use the Least Recently Used (LRU) replacement algorithm.

Four independent execution units are used:

1. Branch Processing Unit (BPU)

2. Integer Unit (IU)

3. Load/Store Unit (LSU)

4. System Register Unit (SRU)

Ethernet

Printer or I/O port

IC Control

SDRAM/DDR Controller

Demodulator

SRAM Interface

PCI Bus

ATA Interface

SIU

Transport &

Video Decoder/

Audio

SDRAM

SDRAM

Video

Graphics

Encoder

Flash,

Boot ROM

IDE Disk

Interface

Memory

Controller

MPC5200

Control SRAM

DMA

Embedded

e300 Core

(MPC603e)

AC97

Debug Interface

PSC1

PSC2

PSC3

USB

I

2

C1

PSC4

ENET

PSC5

PSC6

UART

Codec

UART

IrDA Rx/Tx

Loading...

Loading...