MPC5200B Users Guide, Rev. 1

5-2 Freescale Semiconductor

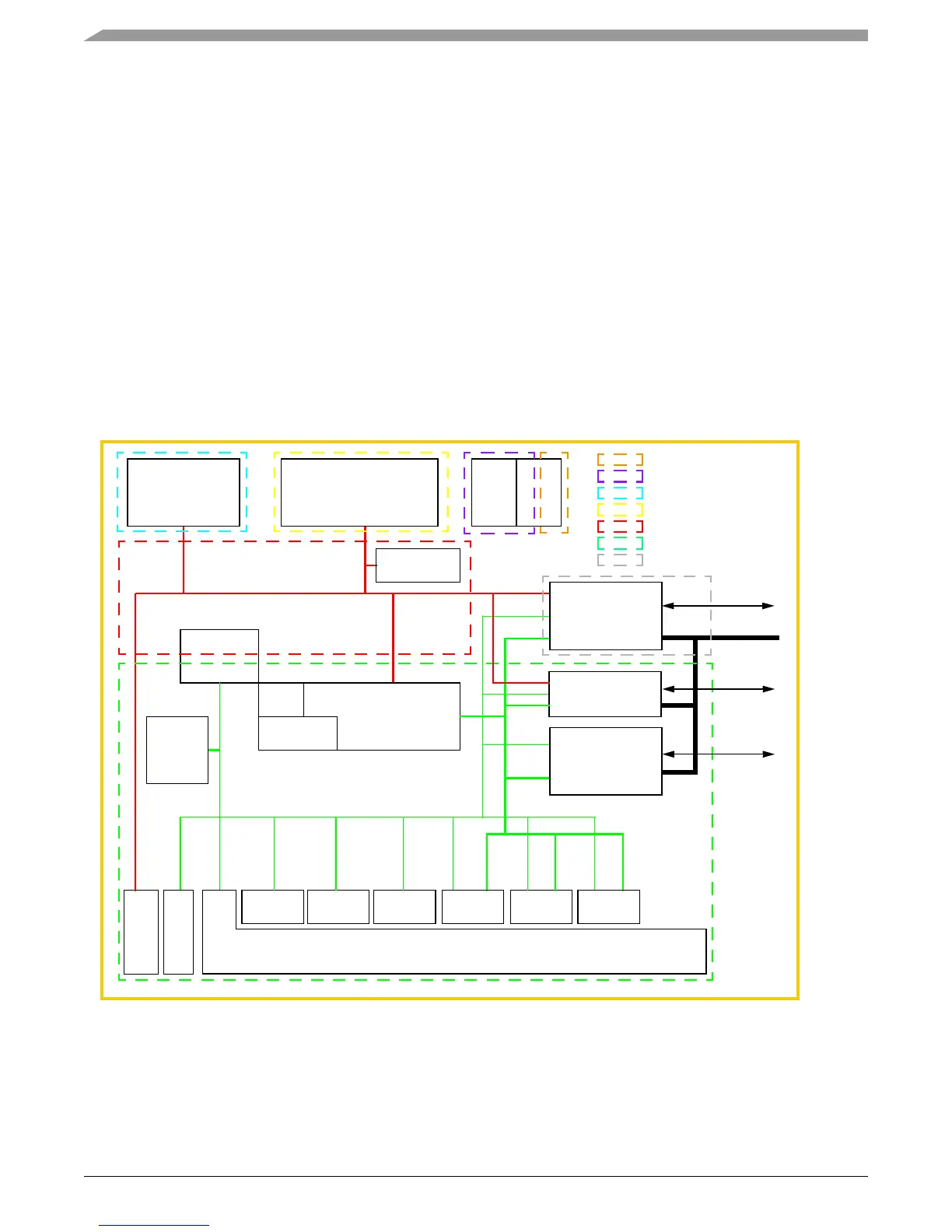

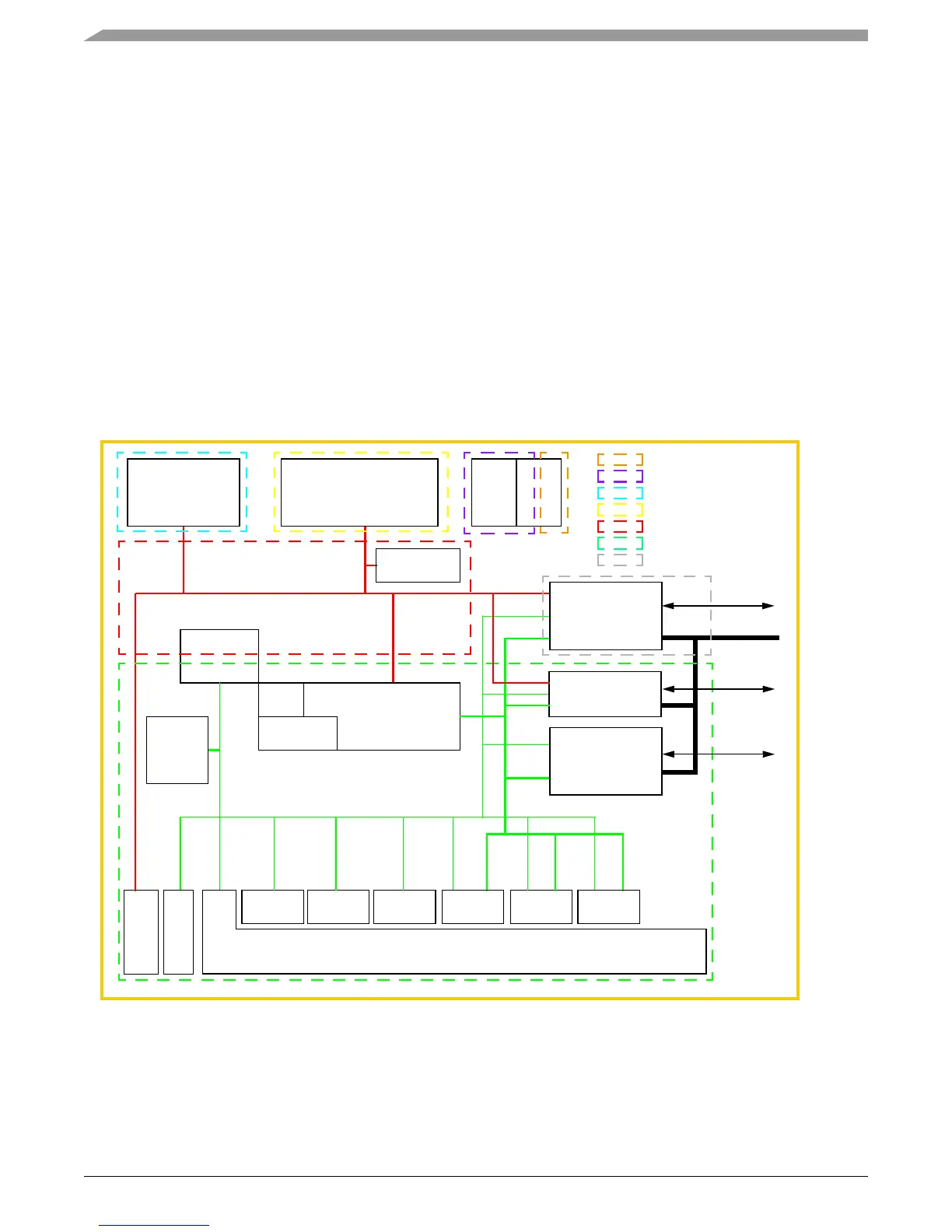

MPC5200B Clock Domains

— When generated externally, the frequency can be different

NOTE

Only one pin is allocated to supply the USB and PSC6/IrDA clock. If both modules require external

clock generation, the frequency must be 48MHz.

SPI—The SPI (Serial Peripheral Interface) has a clock input pin, SPI_CLK. When the SPI is configured as a slave, the clock is

supplied externally. The SPI module therefore has a small asynchronous clock domain.

I

2

C—There are two I

2

C (Inter-Integrated Circuit) modules on MPC5200B. Both have input source clocks (I

2

Cx_CLK) and

therefore asynchronous clock domains.

RTC—The RTC (Real-Time Clock) has its own clock domain, clocked by an external 32.768KHz oscillator. The two oscillator pins

are RTC_XTAL_IN and RTC_XTAL_OUT. There is an asynchronous boundary between this clock domain and the IPB register

interface.

JTAG—The JTAG (Joint Test Action Group) has its own clock domain clocked by the JTAG_TCK pin.

The following peripheral functions use clocks generated from CDM.

MSCAN—The MSCAN (Freescale [formerly Motorola] Scalable Controller Area Network) internal baud rate generator also uses

the ipb_clk or can be derived from the oscillator clock sys_xtal_in. The resultant divided clock samples an incoming CAN data stream

and generates an outgoing data stream.

Figure 5-1. Primary Synchronous Clock Domains

J1850

SPI

PSC_1 -

I

2

C_1

I

2

C_2

MSCAN1

USB GPIO

PERIPHERAL/FUNCTIONAL PIN MUXING

IPBI

IPB

Shared External Bus

ATA

Control

Local Bus

Control

XLB

XLB

IPB

IPB

MEM_CLK Clock Domain

IPB_CLK Clock Domain

GPIO WKUP

CommBus

CommBus

PCI Bus

Control

XLB_CLK Clock Domain

PCI_CLK Clock Domain

Processor Clock Domain

LocalPlus Bus

Controller

ATA

Controller

PCI Bus

Controller

BestComm

DMA

CONF

REG

BestComm

SRAM

SIO

timers

interrupt

e300 Core

SDRAM / DDR

Memory Controller

System

PLL

Clock

Divider

XL Bus

Arbiter

PSC_6

SYS_XTAL Clock Domain

VCO Clock Domain

MSCAN2

Ethernet

Loading...

Loading...