General Purpose Timers (GPT)

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 7-59

7.4.4.2 GPT 0 Counter Input Register—MBAR + 0x0604

GPT 1 Counter Input Register—MBAR + 0x0614

GPT 2 Counter Input Register—MBAR + 0x0624

GPT 3 Counter Input Register—MBAR + 0x0634

GPT 4 Counter Input Register—MBAR + 0x0644

GPT 5 Counter Input Register—MBAR + 0x0654

GPT 6 Counter Input Register—MBAR + 0x0664

GPT 7 Counter Input Register—MBAR + 0x0674

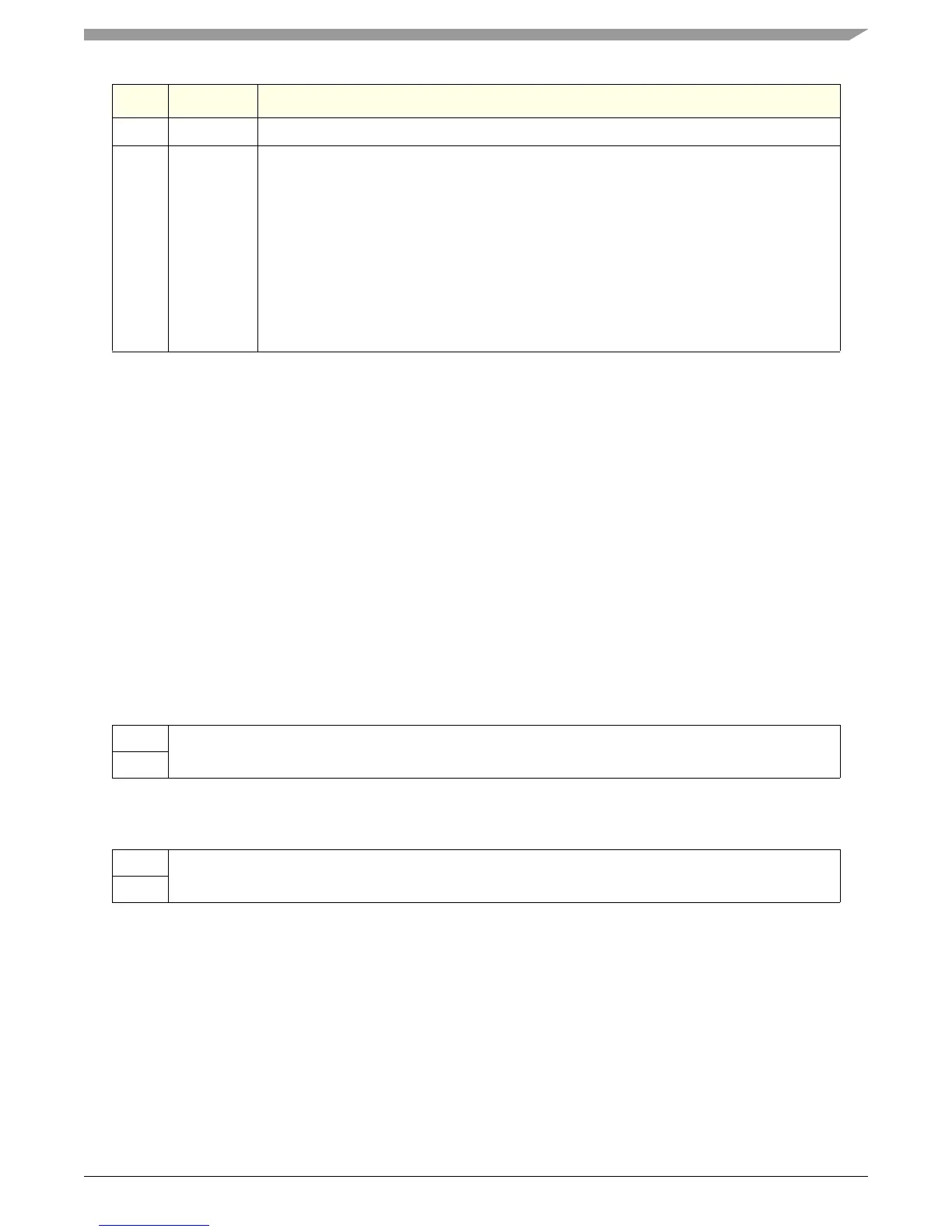

28 — Reserved

29:31 Timer_MS Timer Mode Select (and module enable).

000=Timer module not enabled. Associated I/O pin is in input state. All Timer operation is

completely disabled. Control and status registers are still accessible. This mode should be

entered when timer is to be re-configured, except where the user does not want the I/O pin

to become an input.

001=Timer enabled for input capture.

010=Timer enabled for output compare.

011=Timer enabled for PWM.

1xx=timer enabled for simple GPIO. Internal timer modes available. CE bit controls timer

counter.

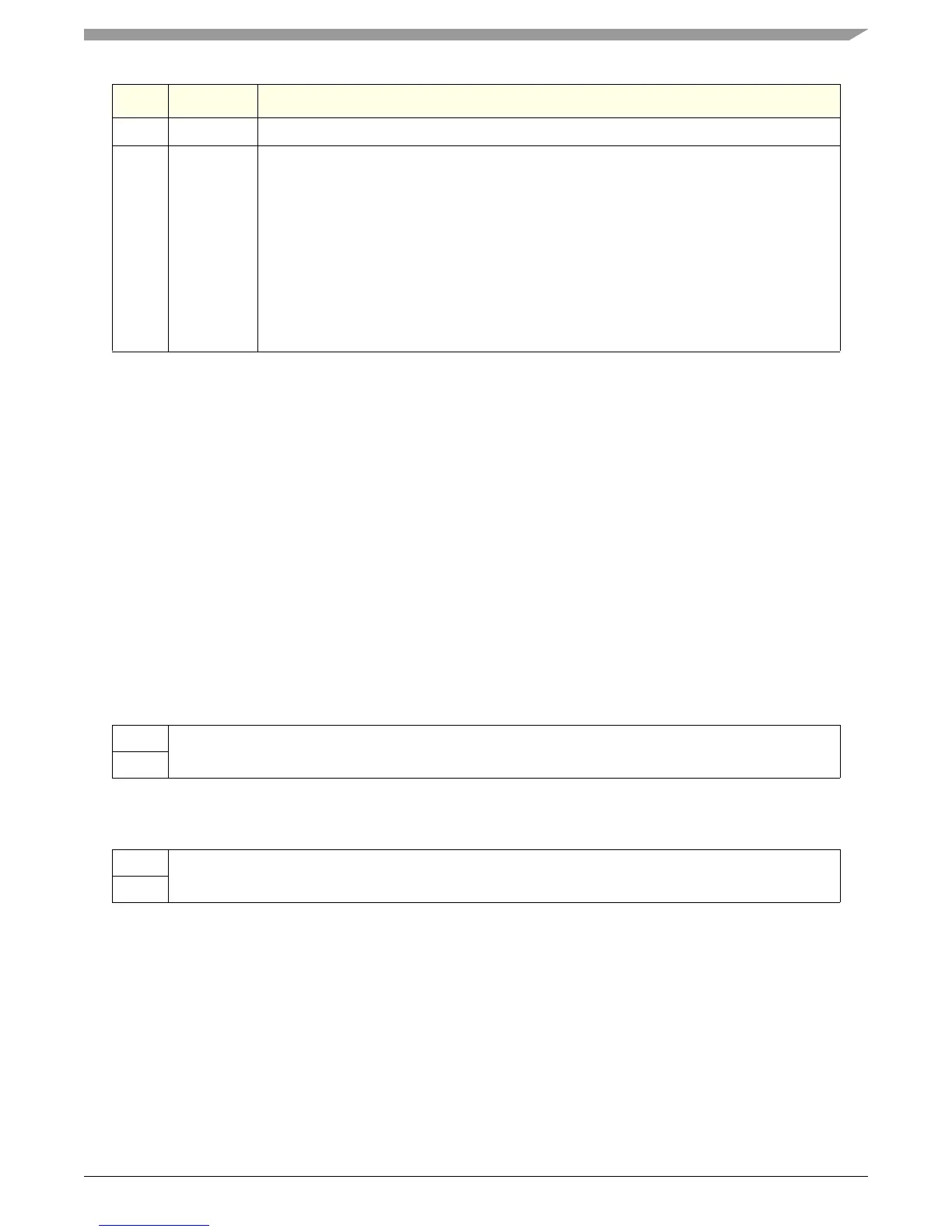

Table 7-48. GPT 0 Counter Input Register

GPT 1 Counter Input Register

GPT 2 Counter Input Register

GPT 3 Counter Input Register

GPT 4 Counter Input Register

GPT 5 Counter Input Register

GPT 6 Counter Input Register

GPT 7 Counter Input Register

msb 012345678 9 101112131415

RPrescale

W

RESET:0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R Count

W

RESET:0 00000000 0 0 0 00 0 0

Bit Name Description

Loading...

Loading...