BestComm DMA Registers—MBAR+0x1200

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 13-27

It must be noted that even if a breakpoint is issued at a specific address the SDMA engine will halt ONLY at a “data aligned” boundary (for

instance, if the task moves 32 bits of data per transaction and a breakpoint is set at address 0x02 then the task will be halted at offset 0x04).

13.15.32 SDMA Debug Module Status Register—MBAR + 0x127C

Table 13-35. EU Breakpoint encoding

EU3 EU2 EU1 EU0

Reset0000

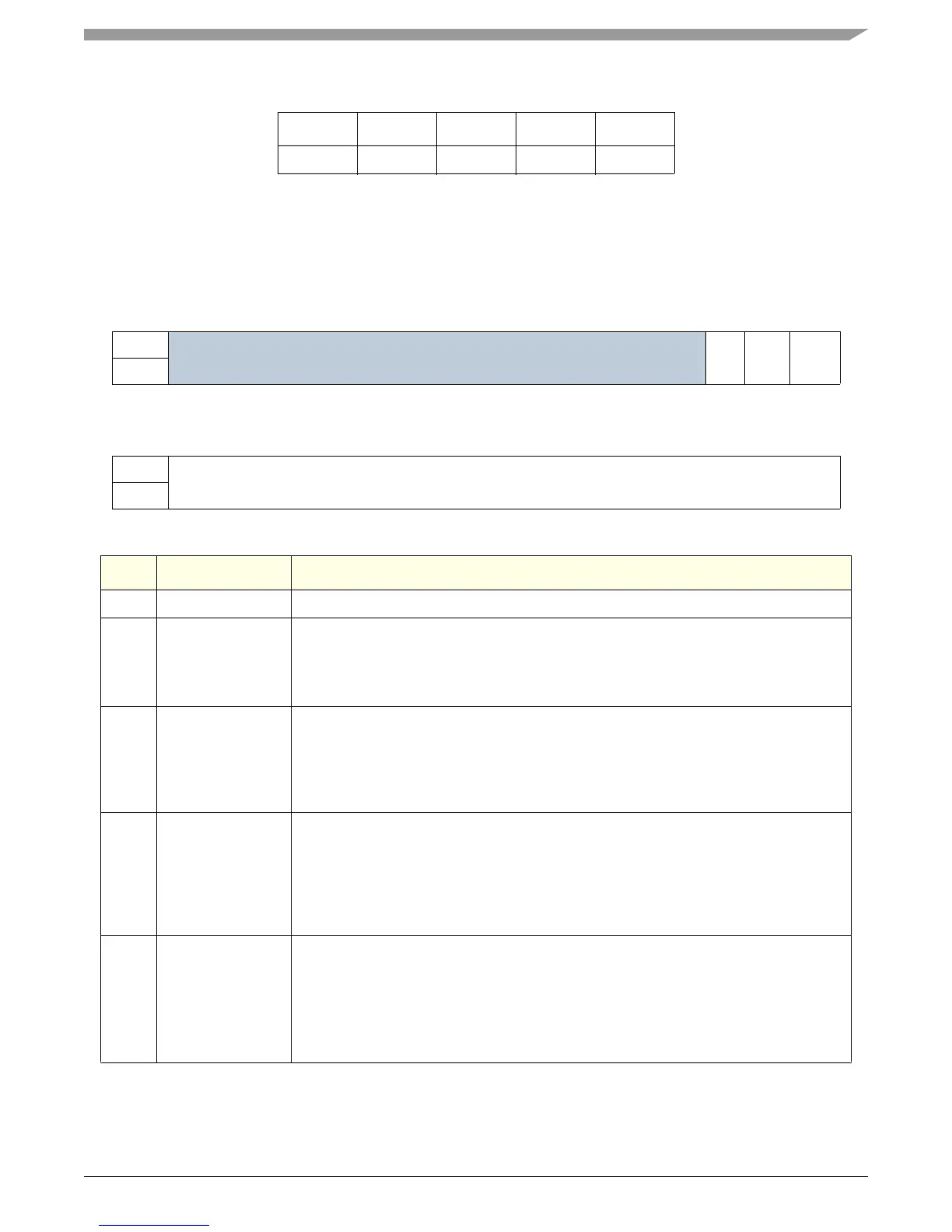

Table 13-36. SDMA Debug Module Status Register

msb 012345678 9 1011121314 15

R

Reserved I E T

W

RESET:0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R dbgStatusReg[15:0]

W

RESET:0 00000000 0 0 0 00 0 0

Bit Name Description

0:12 Reserved Reserved

13 I Interrupt—This bit indicates whether or not an interrupt has been taken. This bit is set to 0

at reset. It can be written by the user or the SDMA engine.

0 No Interrupt

1 Interrupt taken

14 E External Breakpoint—This bit indicates detection of an external breakpoint. Status bit is

sticky and requires a one (1) to be written to it to clear it. The writing of a zero (0) to this bit

has no effect. This bit is set to zero (0) at reset.

0 No external breakpoint detected

1 External breakpoint detected

15 T Triggered (dbgStatusReg[16])—This bit indicates that a SmartDMA breakpoint has

occurred with the current settings. Status bit is sticky and requires a one (1) to be written

to it to clear it. The writing of a zero (0) to this bit has no effect. This bit is set to zero (0) at

reset.

0 Armed or normal operation

1 Triggered or debug mode

16:31 dbgStatusReg[15:0] dbgTaskBlock (dbgStatusReg[15:0])—Each bit corresponds to one of the 16 task numbers.

The value of the register bit reflects the debug state of the task number. A bit is cleared by

writing a one to that bit location; writing a zero (0) has no effect. At system reset, all bits

are initialized to logic zeros (0).

0 Unblocked or normal operation

1 Blocked, task has been blocked due to a breakpoint

Loading...

Loading...