Memory Map / Register Definition

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 19-17

19.5.15 MSCAN Receive Error Counter Register (CANRXERR)-MBAR + 0x091C / 0x099C

READ: Only when in Sleep Mode (SLPRQ = 1 and SLPAK = 1) or Initialization Mode (INITRQ = 1 and INITAK =1).

WRITE: Unimplemented

NOTE

Reading this register when in any other mode other than sleep or Initialization may return an incorrect

value.

NOTE

Writing to these registers when in special modes can alter the MSCAN functionality.

19.5.16 MSCAN Transmit Error Counter Register (CANTXERR)-MBAR + 0x091D/0x099D

Note: This register reflects the status of the MSCAN transmit error counter.

READ: Only when in Sleep Mode (SLPRQ = 1 and SLPAK = 1) or Initialization Mode (INITRQ = 1 and INITAK =1).

WRITE: Unimplemented

NOTE

Reading this register when in any other mode other than sleep or Initialization may return an incorrect

value.

NOTE

Writing to these registers when in special modes can alter the MSCAN functionality.

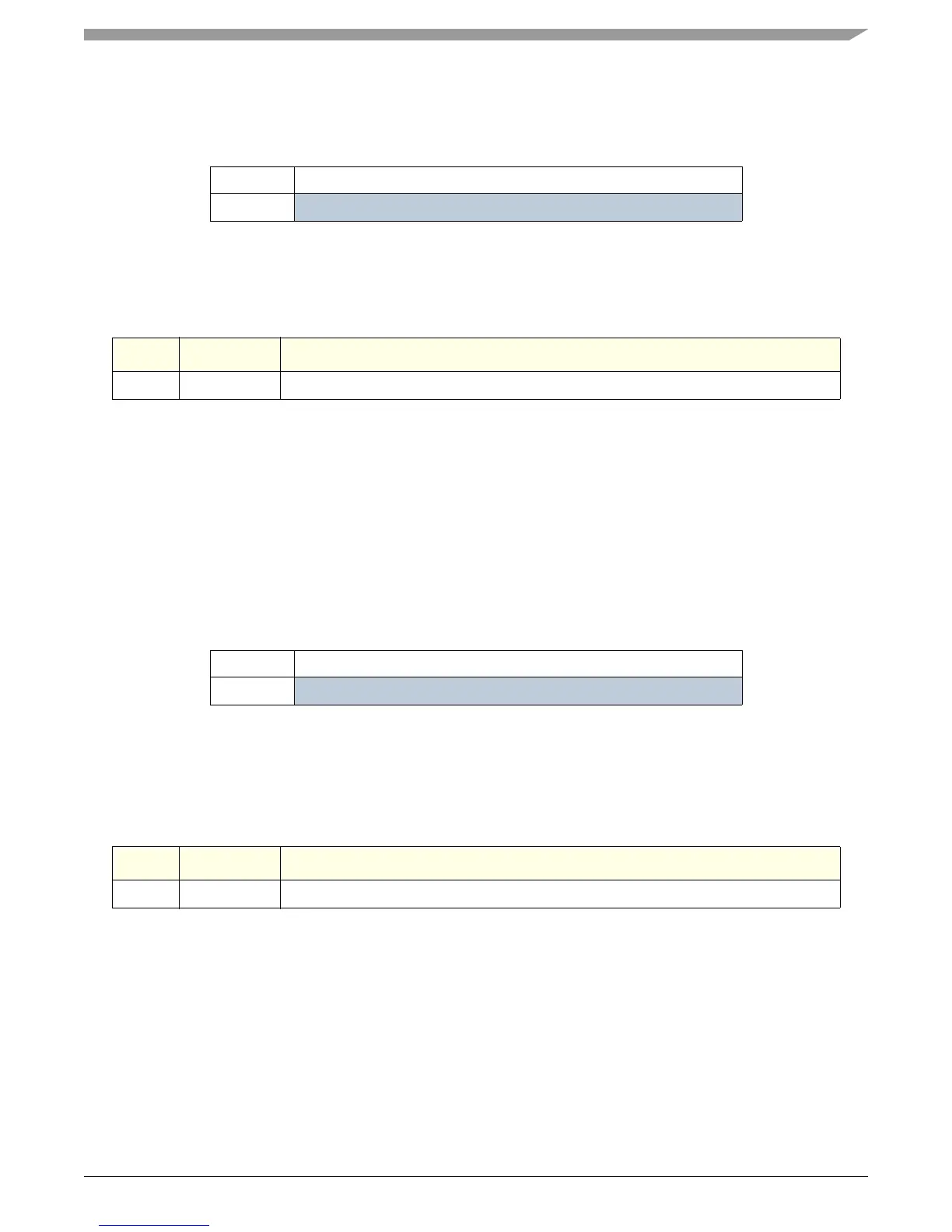

Table 19-20. MSCAN Receive Error Counter Register

msb 01234567 lsb

R RxERR[7:0]

W

RESET:00000000

Bit Name Description

0:7 RxERR[7:0] This register reflects the status of the MSCAN receive error counter.

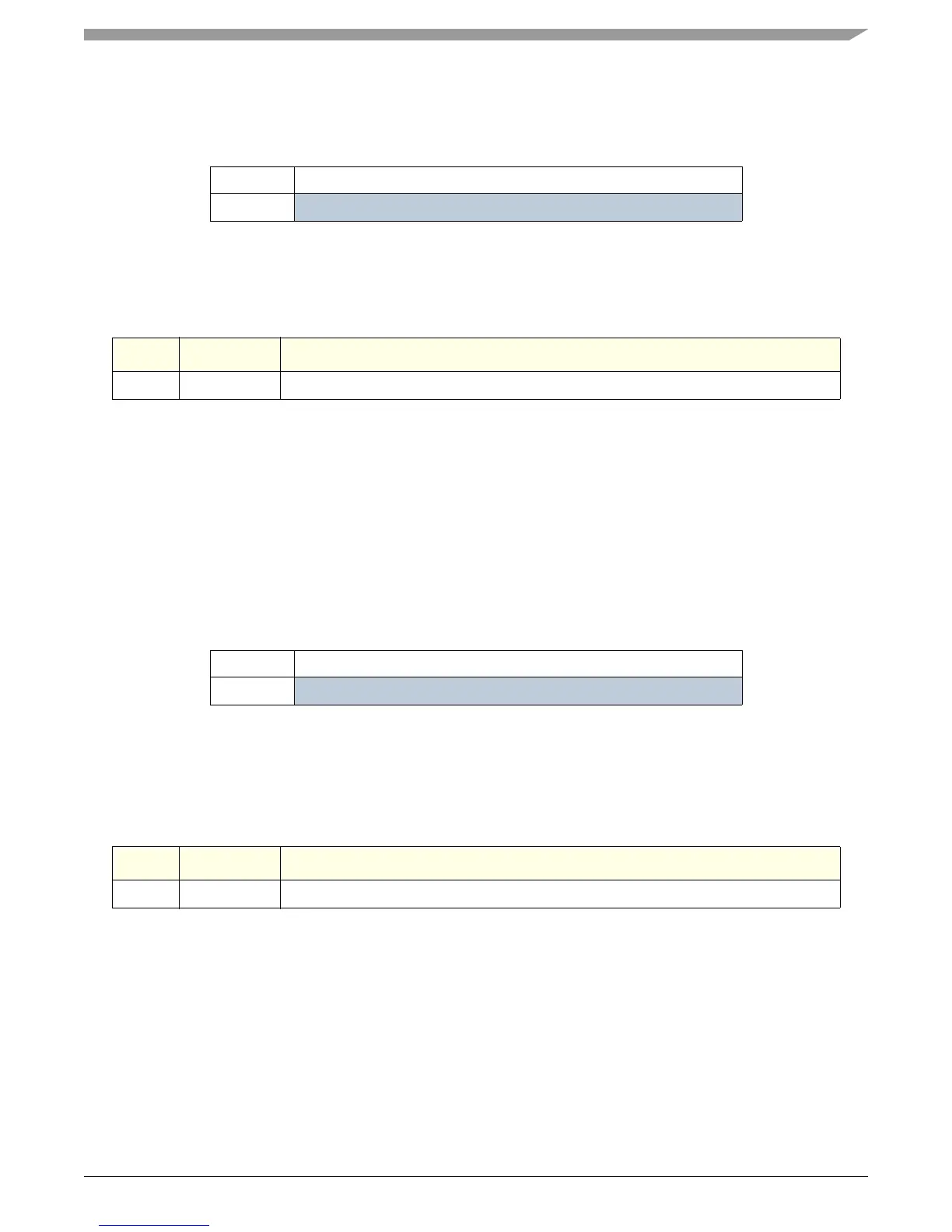

Table 19-21. MSCAN Transmit Error Counter Register

msb 01234567 lsb

R TxERR[7:0]

W

RESET:00000000

Bit Name Description

0:7 TxERR[7:0] This register reflects the status of the MSCAN transmit error counter.

Loading...

Loading...