Pinout Tables

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 2-47

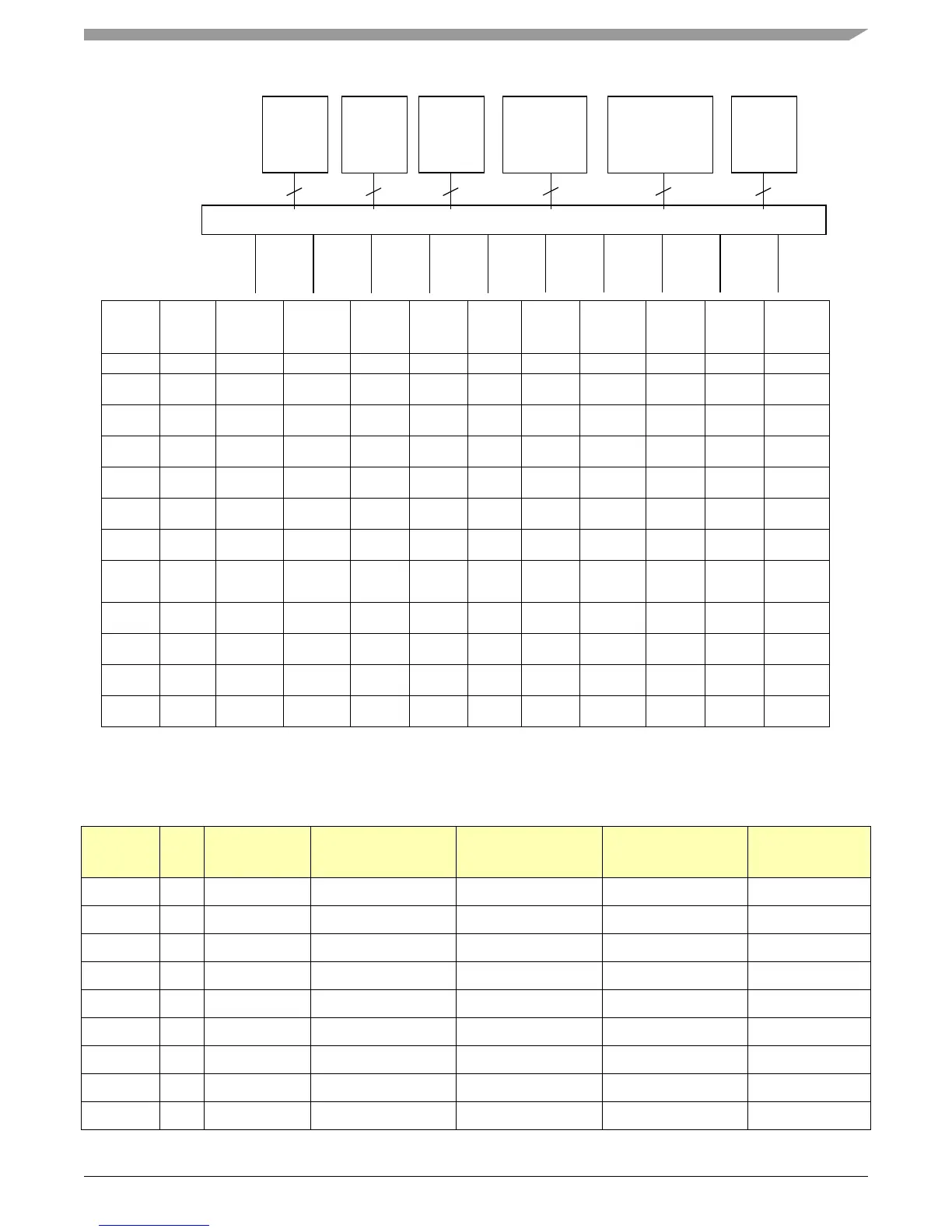

Figure 2-9. Ethernet Input / Control Port Map—10 Pins

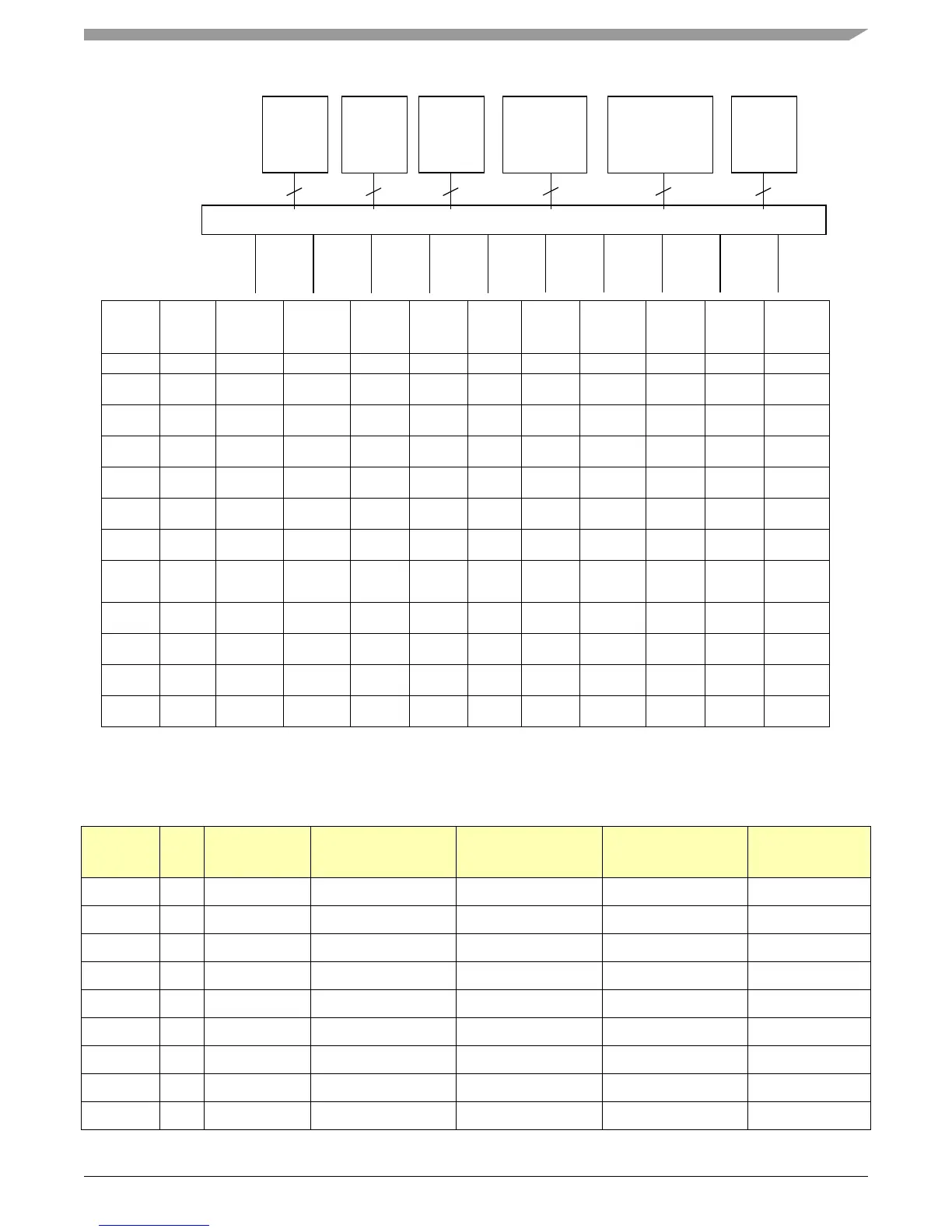

Table 2-18. Ethernet Pin Functions

Pin name Dir.

Reset

Configuration

GPIO USB2 ETH7 ETH7 / USB2

ETH_0 I/O RST_CFG8 OUTPUT OUTPUT ETH7_TXEN ETH7_TXEN

ETH_1 I/O RST_CFG15 OUTPUT OUTPUT ETH7_TXD_0 ETH7_TXD_0

ETH_2 I/O RST_CFG10 OUTPUT USB2_TXP OUTPUT USB2_TXP

ETH_3 I/O RST_CFG11 OUTPUT USB2_PRTPWR OUTPUT USB2_PRTPWR

ETH_4 I/O RST_CFG12 OUTPUT USB2_SPEED OUTPUT USB2_SPEED

ETH_5 I/O RST_CFG13 OUTPUT USB2_SUSPEND OUTPUT USB2_SUSPEND

ETH_6 I/O RST_CFG14 OUTPUT USB2_OE OUTPUT USB2_OE

ETH_7 I/O OUTPUT USB2_TXN OUTPUT USB2_TXN

ETH_8 I/O GPIO GPIO ETH7__CD ETH7__CD

GPIO

Ethernet

USB2

(I/O portion)(Inputs)

Pin Drivers and MUX Logic

9

ETH_13 ETH_14 ETH_15 ETH_16 ETH_17

10

ETH_8 ETH_9 ETH_10 ETH_11 ETH_12

4

PSC5

5

PSC4

5

J1850

2

Function

Port_

conf

[12:15]

ETH_8 ETH_9 ETH_10 ETH_11 ETH_12 ETH_13 ETH_14 ETH_15 ETH_16 ETH_17

RST_CFG

GPIO 0000 OUTPUT OUTPUT OUTPUT OUTPUT INTERRUPT INTERRUPT INTERRUPT INTERRUPT GPIO_W/WAK

E_UP

USB2 0001 OUTPUT OUTPUT OUTPUT OUTPUT USB2_RXD USB2_RXP USB2_RXN USB2_OVR

CNT

GPIO_W/WAK

E_UP

ETH7 0010 ETH7_CD ETH7_RXCLK ETH7_COL ETH7_TXCL

K

ETH7_RXD

_0

INTERRUPT INTERRUPT INTERRUPT INTERRUPT GPIO_W/WAK

E_UP

ETH7 / USB2 0011 ETH7_CD ETH7_RXCLK ETH7_COL ETH7_TXCL

K

ETH7_RXD

_0

USB2_RXD USB2_RXP USB2_RXN USB2_OVR

CNT

GPIO_W/WAK

E_UP

ETH_18 no

MD

0100 ETH18_RXDV ETH18_RXCL

K

ETH18_COL ETH18_TXC

LK

ETH18_RX

D_0

ETH18_RXD

_1

ETH18_RXD_

2

ETH18_RXD

_3

ETH18_RXE

RR

ETH18_CRS

ETH_18 w/

MD

0101 ETH18_w/MD_

RXDV

ETH18_w/MD_

RXCLK

ETH18_w/M

D_COL

ETH18_TXD ETH18_w/

MD_RXD_0

ETH18_w/M

D_RXD_1

ETH18_w/MD

_RXD_2

ETH18_w/M

D_RXD_3

ETH18_w/M

D_RXERR

ETH18_W/MD

_CRS

ETH7 /

UART4e/J18

50

1000 ETH7_CD ETH7_RXCLK ETH7_COL ETH7_TXCL

K

ETH7_RXD

_0

J1850_RX UART4e_RXD UART4e_CT

S

UART4_DCD GPIO_W/WAK

E_UP

ETH7 /J1850 1001 ETH7_CD ETH7_RXCLK ETH7_COL ETH7_TXCL

K

ETH7_RXD

_0

J1850_RX INTERRUPT INTERRUPT INTERRUPT GPIO_W/WAK

E_UP

UART4/5e/J1

850

1010 UART5e_CD UART5e_CTS OUTPUT OUTPUT UART5e_R

XD

J1850_RX UART4_RXD UART4_CTS UART4_CD GPIO_W/WAK

E_UP

UART5e/J18

50

1011 UART5e_DCD UART5e_CTS OUTPUT OUTPUT UART5e_R

XD

J1850_RX INTERRUPT INTERRUPT INTERRUPT GPIO_W/WAK

E_UP

J1850 1100 GPIO OUTPUT OUTPUT OUTPUT J1850_RX INTERRUPT INTERRUPT INTERRUPT GPIO_W/WAK

E_UP

Loading...

Loading...