Host Control (HC) Operational Registers

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 12-21

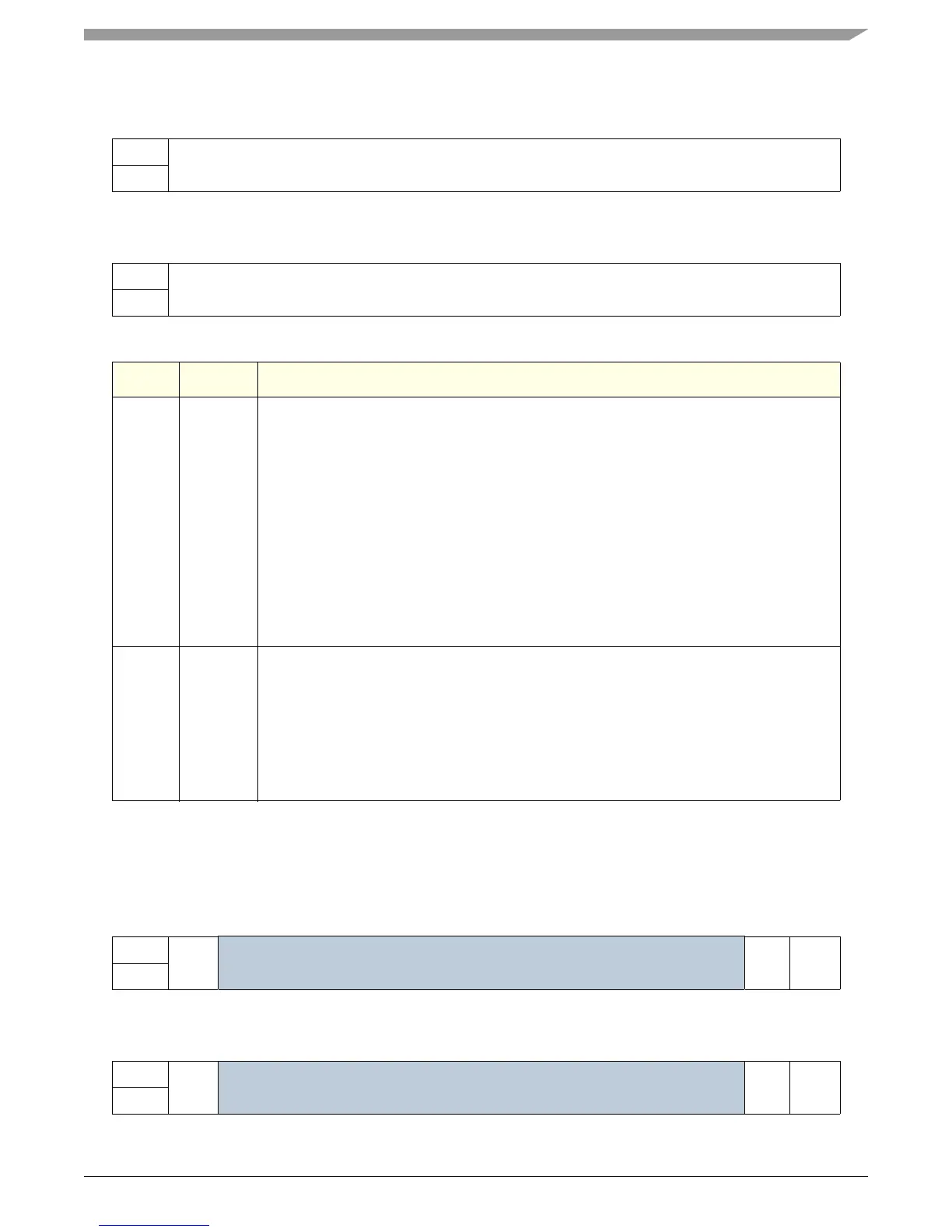

12.4.5.3 USB HC Rh Status Register—MBAR + 0x1050

This register is divided into two parts. The lower 16 bits of a 32-bit word represents the hub status field; the upper word represents the hub

status change field. Reserved bits should always be written 0.

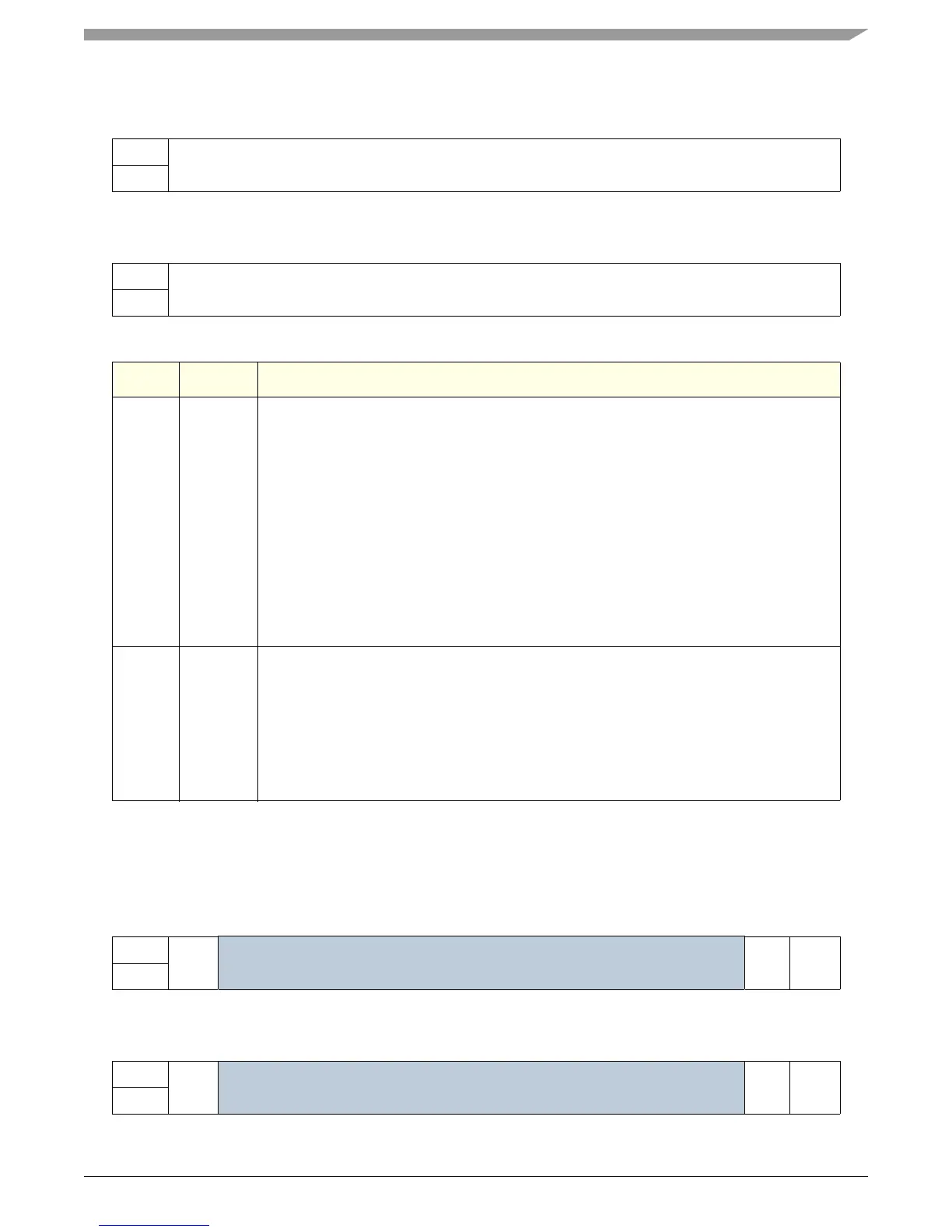

Table 12-20. USB HC Rh Descriptor B Register

msb 012345678 9 1011121314 15

R PPCM

W

RESET:0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

RDR

W

RESET:0 00000000 0 0 0 00 0 0

Bits Name Description

0:15 PPCM PortPowerControlMask—each bit indicates whether a port is affected by a global power

control command when PSM is set.

• When set, port power state is only affected by per-port power control

( Set / Clear PortPower ).

• When cleared, port is controlled by the global power switch

(Set/ClearGlobalPower).

If device is configured to Global Switching Mode (PSM=0), this field is not valid.

bit 0—Reserved

bit 1—Ganged-power mask on Port #1

bit 2—Ganged-power mask on Port #2

…

bit15—Ganged-power mask on Port #15

16:31 DR NDeviceRemovable—each bit is dedicated to a Root Hub port. When cleared, the attached

device is removable. When set, the attached device is not removable.

bit 0—Reserved

bit 1—Device attached to Port #1

bit 2—Device attached to Port #2

…

bit15—Device attached to Port #15

Table 12-21. USB HC Rh Status Register

msb 012345678 9 1011121314 15

RCRWE

Reserved OCIC LPSC

W

RESET:0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

RDRWE

Reserved OCI LPS

W

RESET:0 00000000 0 0 0 00 0 0

Loading...

Loading...