MPC5200B Users Guide, Rev. 1

14-16 Freescale Semiconductor

FEC Registers—MBAR + 0x3000

14.5.6 FEC Ethernet Control Register—MBAR + 0x3024

The ECNTRL register is a read/write user register that can enable/disable the FEC. Some fields may be altered by hardware.

Bits Name Description

0:6 — Reserved

7 X_DES_ACTIVE Set to one when this register is written, regardless of the value written. Cleared by the

FEC device whenever no additional “ready” descriptors remain in the transmit ring.

8:31 — Reserved

Table 14-14. FEC Ethernet Control Register

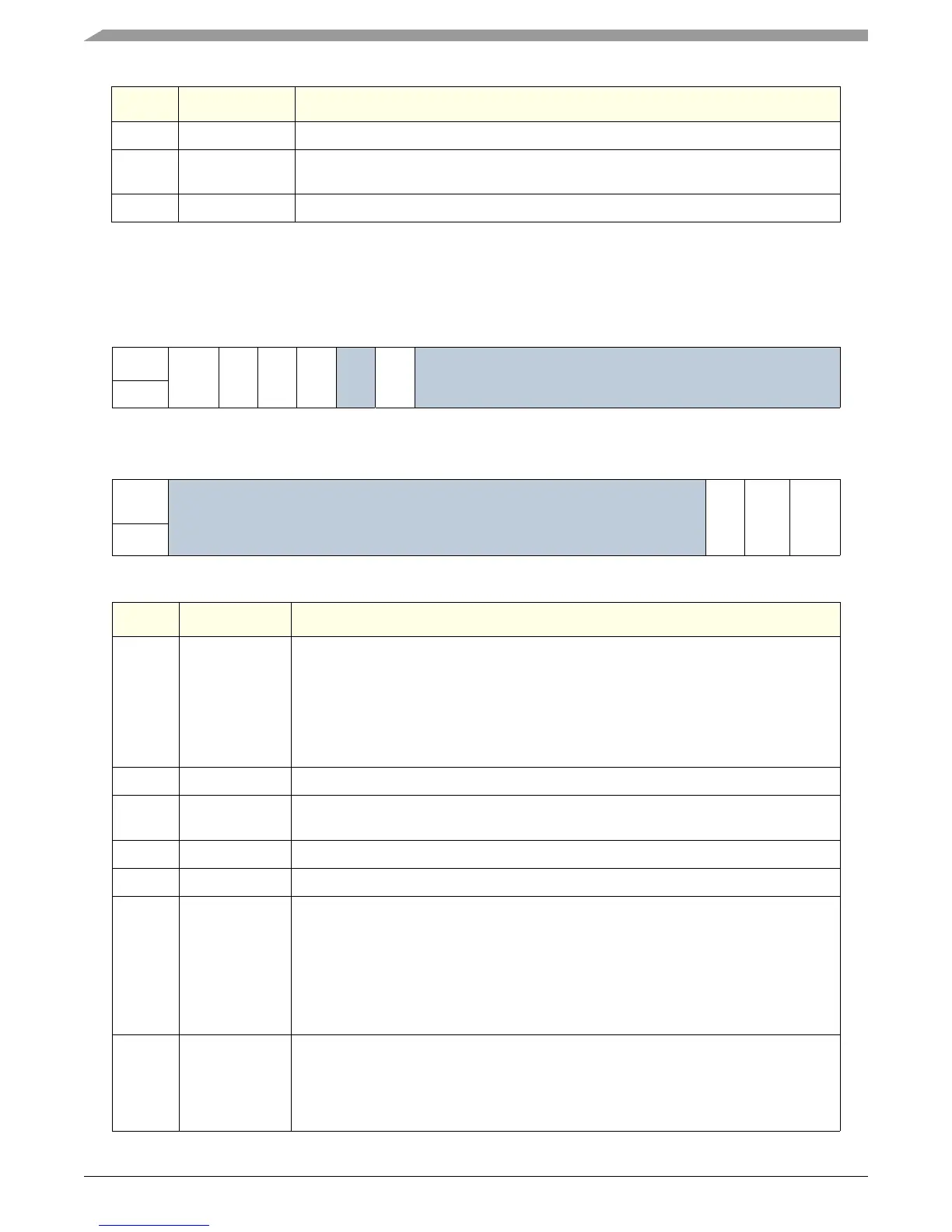

msb 012345678 9 1011121314 15

R

TAG0

TAG1

TAG2

TAG3

Rsvd

TESTMD

Reserved

W

RESET:0 00000000 0 0 0 00 0 0

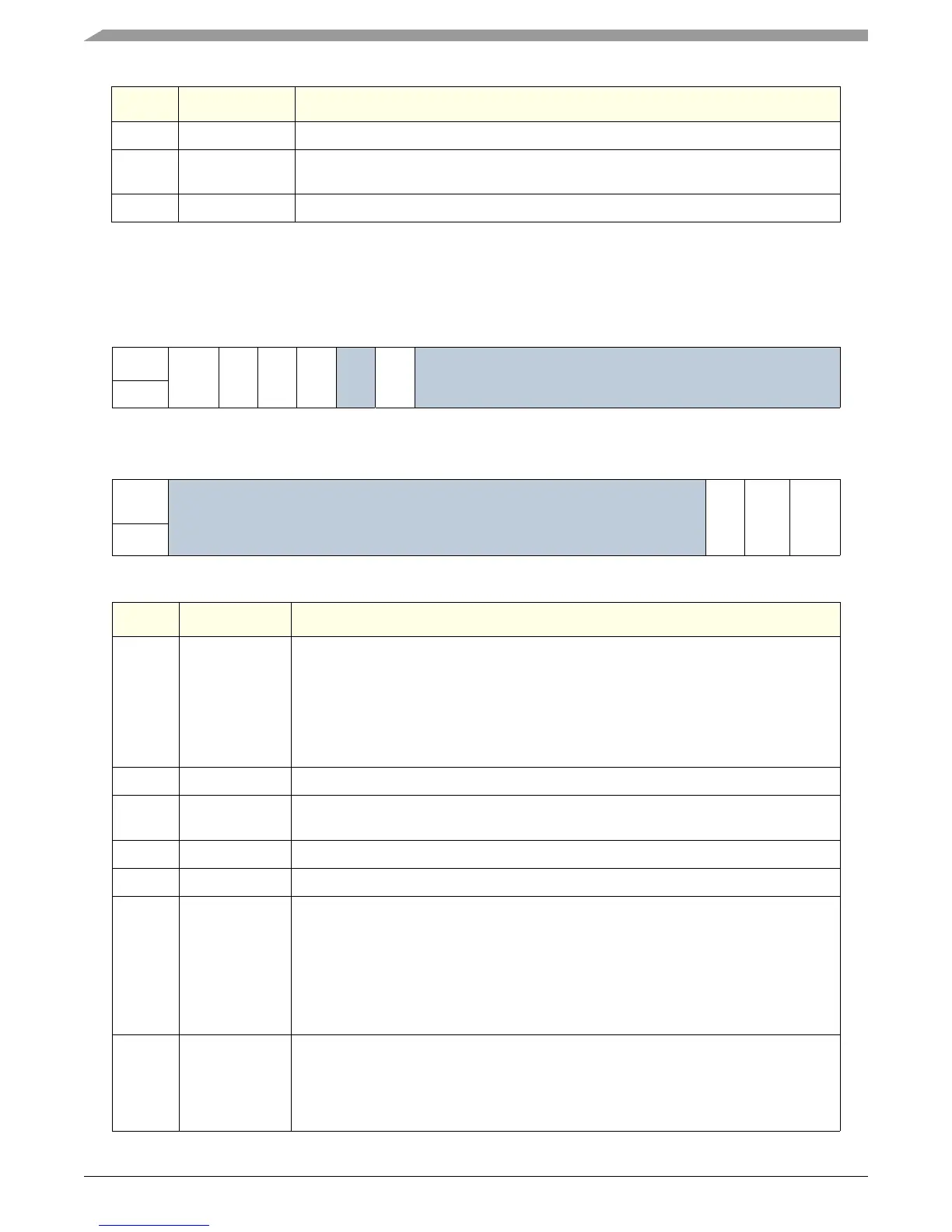

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Reserved

FEC_OE

ETHER_EN

RESET

W

RESET:0 00000000 0 0 0 00 0 0

Bits Name Description

0:3 TAG[0:3] This field allows programming and reading the TBUS tag bits. This field is used for

debug/test only, and is implemented in two separate 4-bit registers. The “tags_in”

register is written to when a write to this register takes place. This field (tags_in) resets

to 1111. During a write cycle to any FEC register other than ECNTRL the tags_in value

is driven onto the tbus data bus tag field. During a read cycle the tbus tag field bits is

latched and saved in the “tags_out” register. When the ECNTRL register is read the value

from “tags_out” shows in the TAG field.

4—Reserved

5 TESTMD Test Mode—used for manufacturing test only. TESTMD resets to 0. This bit forces the

bus controller to ignore all bus requests except the one from the SIF.

6:28 — Reserved

29 FEC_OE FEC Output Enable—It is a spare bit and has no affect on internal operation.

30 ETHER_EN Ethernet Enable—When this bit is set, FEC is enabled and Rx/Tx can occur. When bit is

cleared, Rx stops immediately; Tx stops after a bad CRC is appended to any frame

currently being transmitted. The ETHER_EN bit is altered by hardware under the

following conditions:

• If ECNTRL.RESET is written to 1 by software, ETHER_EN is cleared.

• If error conditions causing the IEVENT.EBERR, XFIFO_ERROR or RFIFO_ERROR

bits to set occur ETHER_EN is cleared.

31 RESET Ethernet Controller Reset—When this bit is set, the equivalent of a hardware reset is

done, but it is local to the FEC. ETHER_EN is cleared and all other FEC registers take

their reset values. Also, any Tx/Rx currently in progress is abruptly aborted. This bit is

automatically cleared by hardware during the reset sequence. The reset sequence takes

approximately 8 clock cycles after RESET is written with 1.

Loading...

Loading...