MPC5200B Users Guide, Rev. 1

14-10 Freescale Semiconductor

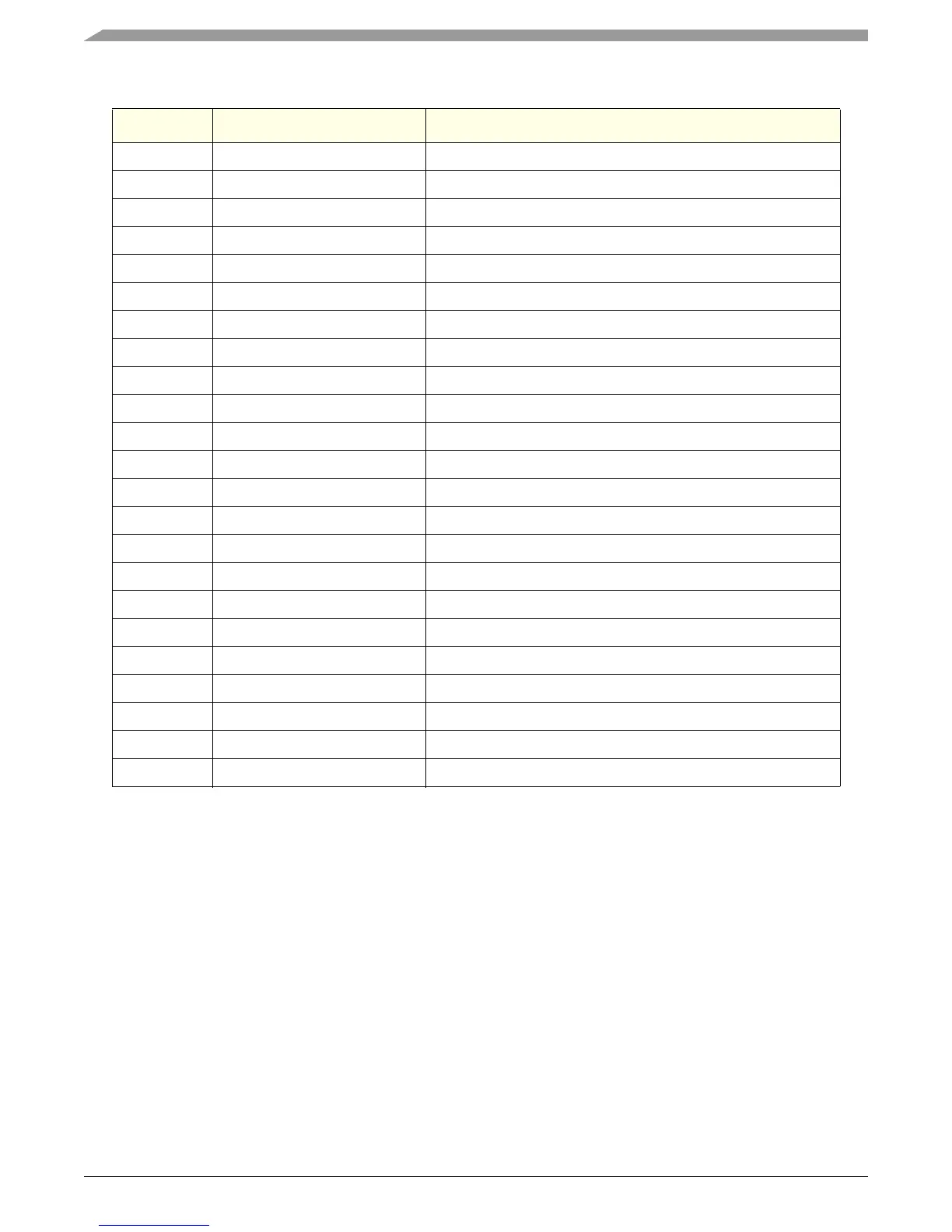

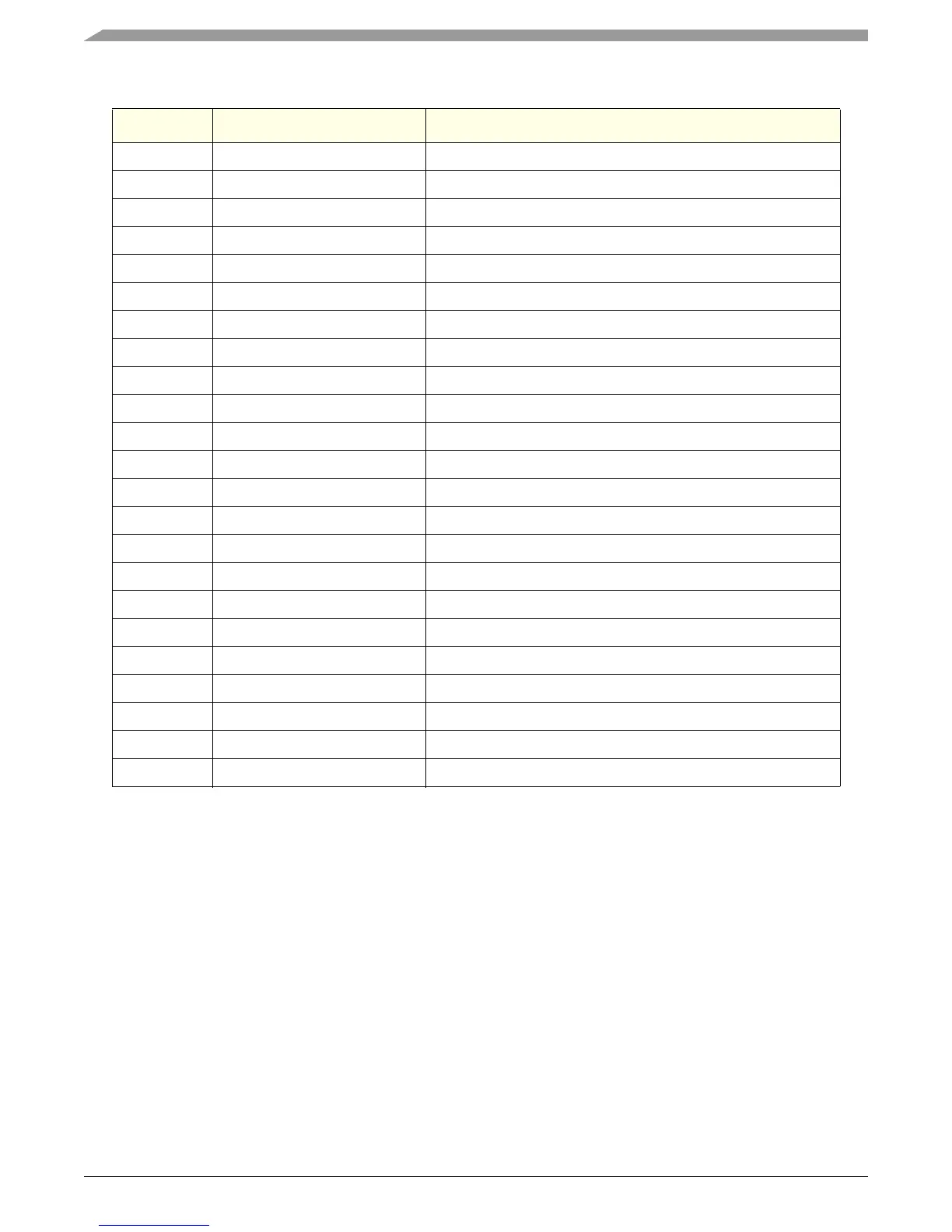

FEC Registers—MBAR + 0x3000

14.5 FEC Registers—MBAR + 0x3000

The FEC uses 37 32-bit registers. These registers are located at an offset from MBAR of 0x3000. Register addresses are relative to this offset.

Therefore, the actual register address is MBAR + 0x3000 + register address

Hyperlinks to the FEC registers are provided below:

290 RMON_R_CRC_ALIGN RMON Rx Packets with CRC/Align error

294 RMON_R_UNDERSIZE RMON Rx Packets less than 64Bytes, good CRC

298 RMON_R_OVERSIZE RMON Rx Packets greater than MAX_FL bytes, good CRC

29C RMON_R_FRAG RMON Rx Packets less than 64Bytes, bad CRC

2A0 RMON_R_JAB RMONRxPackets greater than MAX_FL bytes, bad CRC

2A4 RMON_R_RESVD_0 Reserved

2A8 RMON_R_P64 RMON Rx 64Byte packets

2AC RMON_R_P65TO127 RMON Rx 65 to 127Byte packets

2B0 RMON_R_P128TO255 RMON Rx 128 to 255Byte packets

2B4 RMON_R_P256TO511 RMON Rx 256 to 511Byte packets

2B8 RMON_R_P512TO1023 RMON Rx 512 to 1023Byte packets

2BC RMON_R_P1024TO2047 RMON Rx 1024 to 2047Byte packets

2C0 RMON_R_P_GTE2048 RMON Rx packets with greater than 2048Bytes

2C4 RMON_R_OCTETS RMON Rx Octets

2C8 IEEE_R_DROP Count of frames not counted correctly

2CC IEEE_R_FRAME_OK Frames received OK

2D0 IEEE_R_CRC Frames received with CRC error

2D4 IEEE_R_ALIGN Frames received with alignment error

2D8 IEEE_R_MACERR Rx FIFO overflow count

2DC R_FDXFC Flow Control Pause frames received

2E0 IEEE_R_OCTETS_OK Octet count for frames received without error

2E4–2FC rsvd Reserved

300–3FF rsvd Reserved

Table 14-8. MIB Counters (continued)

Address Mnemonic Description

Loading...

Loading...