XLB Arbiter Registers—MBAR + 0x1F00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 16-11

16.2.11 Arbiter Master Priority Register (R/W)—MBAR + 0x1F68

The Arbiter Master N Priority Register is used to set the software-programmable priority of each master. This register is used in conjunction

with the Arbiter Master Priority Enable Register to enable software-programmable master priorites, consequently ignoring internal,

hardware-wired signals. This register may be written at any time, and changes to this register become effective one clock after the register is

written.

Valid priority values range from 0 to 7, with 0 being the highest priority. Each of the eight fields in the register has the upper (fourth) bit

reserved. This allows for a possible future expansion to 16 priority levels. Currently, the reserved bits will always read as 0, and should be

written as 0 for future software compatibility.

M2 1 BestComm

M1 2 USB

M0 7 e300 Core

Table 16-12. Arbiter Master Priority Register

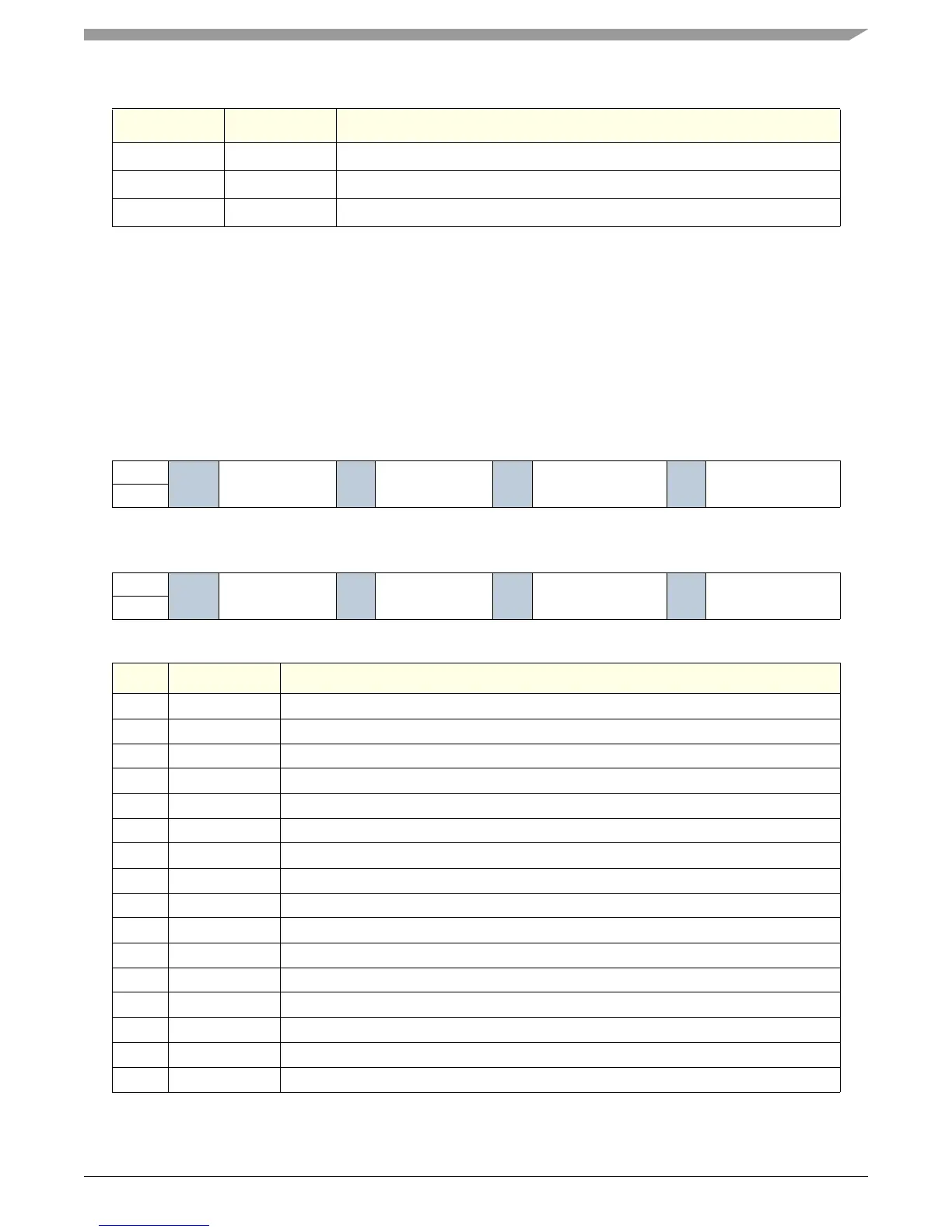

msb 012345678 9 1011121314 15

R Rsvd M7 Priority Rsvd M6 Priority Rsvd M5 Priority Rsvd M4 Priority

W

RESET:0 00100010 0 0 1 00 0 1

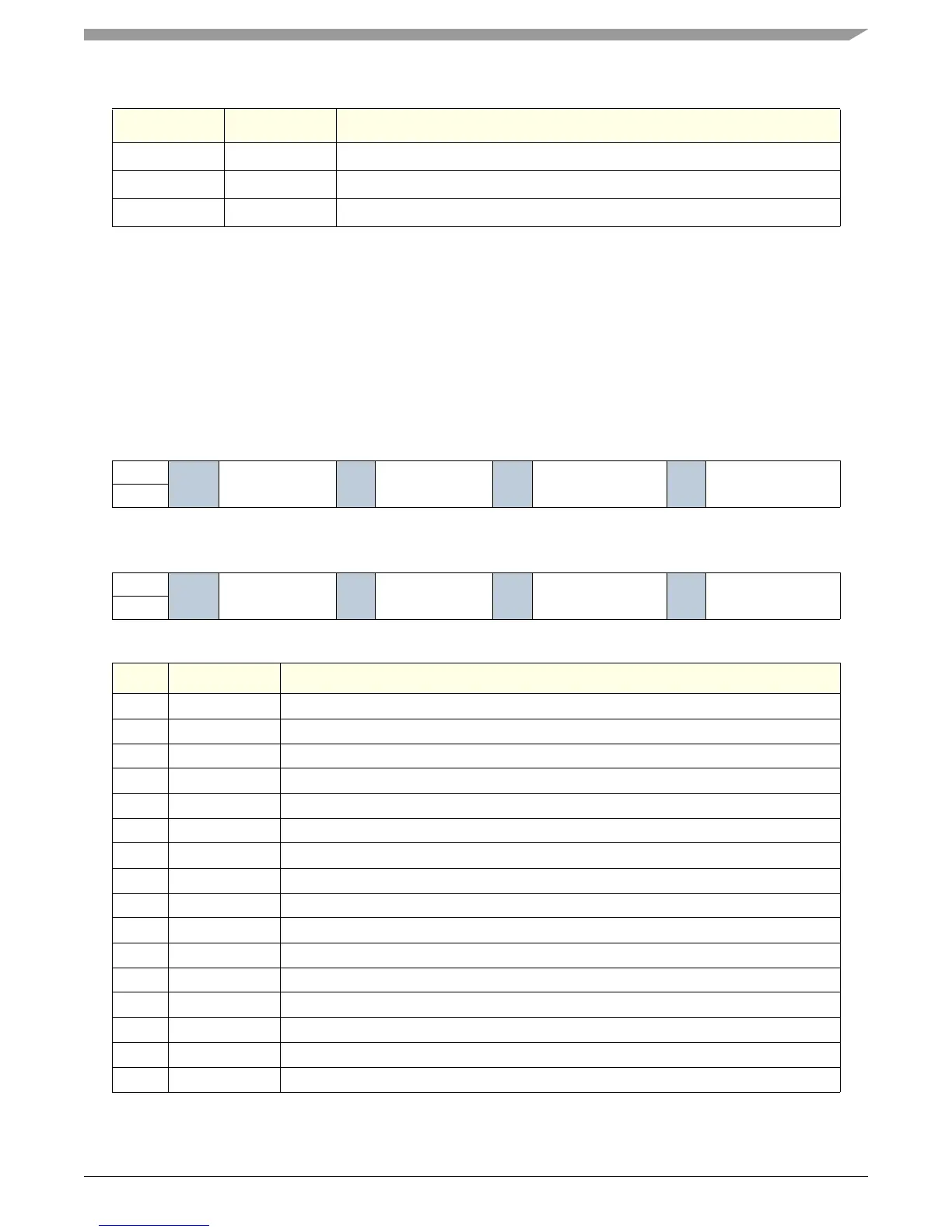

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Rsvd M3 Priority Rsvd M2 Priority Rsvd M1 Priority Rsvd M0 Priority

W

RESET:0 00100010 0 0 1 00 0 0

Bit Name Description

0—Reserved

1:3 M7P Master 7 Priority

4—Reserved

5:7 M6P Master 6 Priority

8—Reserved

9:11 M5P Master 5 Priority

12 — Reserved

13:15 M4P Master 4 Priority

16 — Reserved

17:19 M3P Master 3 Priority

20 — Reserved

21:23 M2P Master 2 Priority

24 — Reserved

25:27 M1P Master 1 Priority

28 — Reserved

29:31 M0P Master 0 Priority

Table 16-11. Hardware Assignments of Master Priority

Master Priority Description

Loading...

Loading...