General Purpose I/O (GPIO)

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 7-49

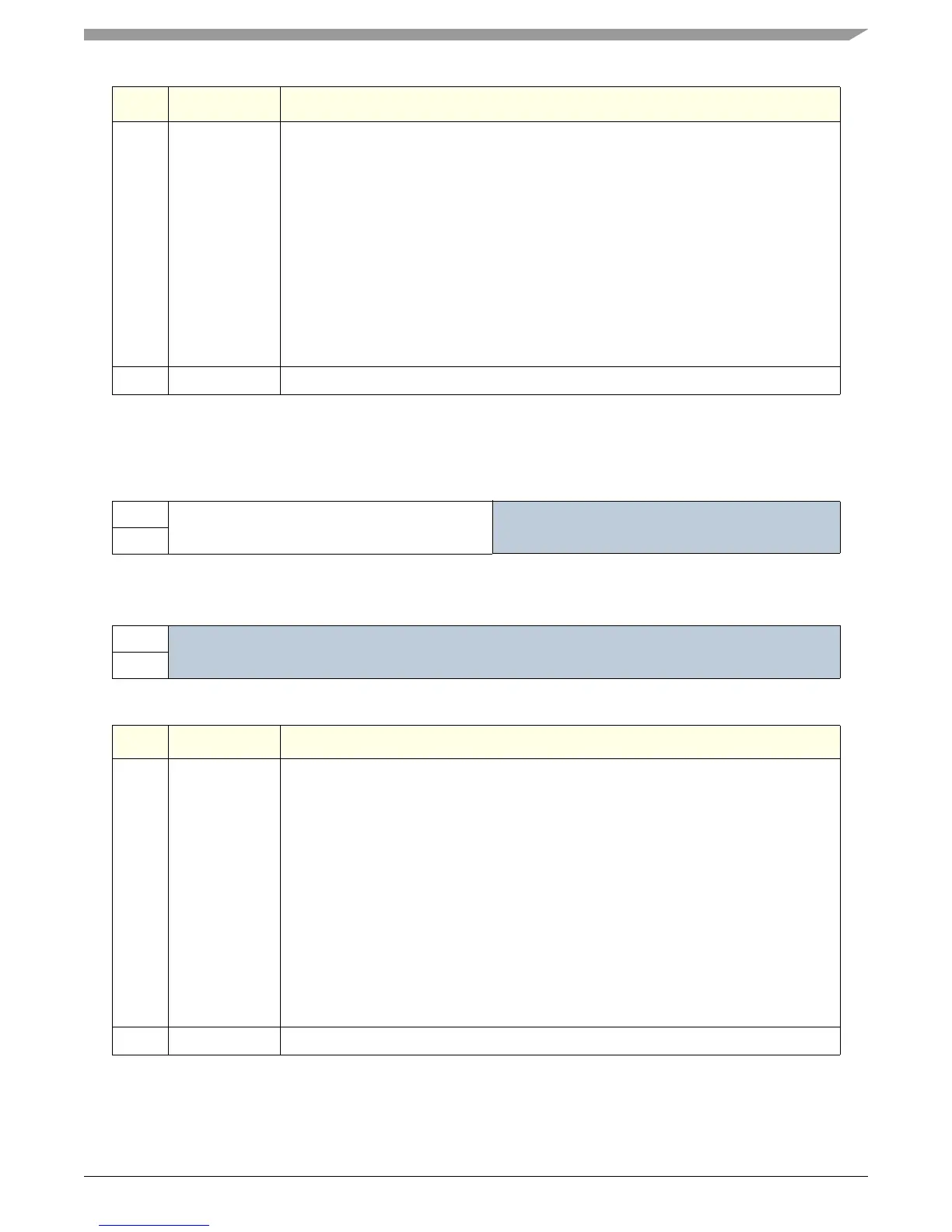

7.3.2.2.4 GPW WakeUp GPIO Data Value Out Register —MBAR + 0x0C0C

Bit Name Description

0:7 WDDR[7:0] Individual bits to control directionality of the pin as GPIO.

Bit 0 controls GPIO_WKUP_7 (GPIO_WKUP_7 pin)

Bit 1 controls GPIO_WKUP_6 (GPIO_WKUP_6 pin)

Bit 2 controls GPIO_WKUP_5 (PSC6_1 pin)

Bit 3 controls GPIO_WKUP_4 (PSC6_0 pin)

Bit 4 controls GPIO_WKUP_3 (ETH_17 pin)

Bit 5 controls GPIO_WKUP_2 (PSC3_9 pin)

Bit 6 controls GPIO_WKUP_1 (PSC2_4 pin)

Bit 7 controls GPIO_WKUP_0 (PSC1_4 pin)

0 = Pin is Input (default).

1 = Pin is Output.

8:31 — Reserved

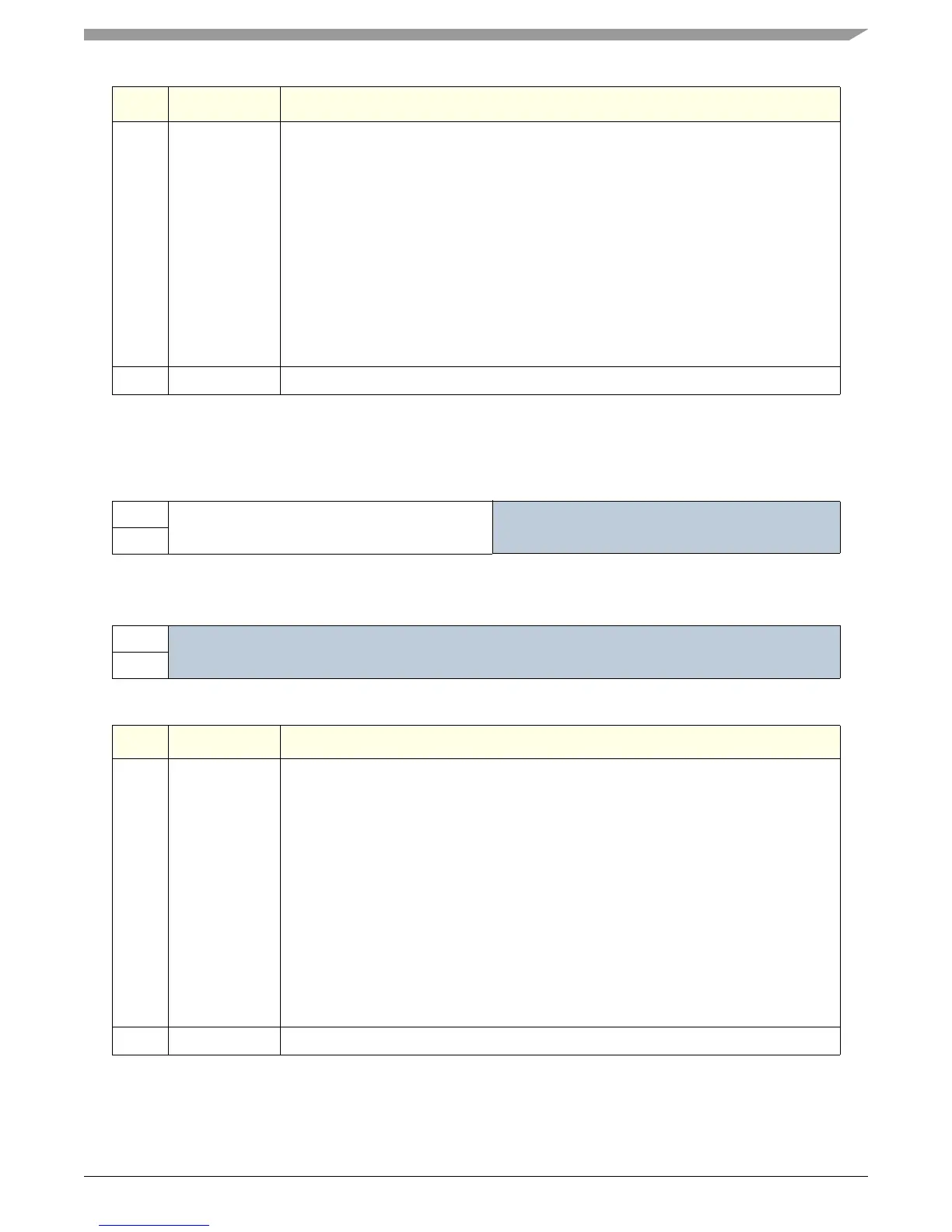

Table 7-40. GPW WakeUp GPIO Data Value Out Register

msb 012345678 9 101112131415

RWDVO

Reserved

W

RESET:0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Reserved

W

RESET:0 00000000 0 0 0 00 0 0

Bit Name Description

0:7 WDVO Individual bits to control the state of pins configured as GPIO output.

Bit 0 controls GPIO_WKUP_7 (GPIO_WKUP_7 pin)

Bit 1 controls GPIO_WKUP_6 (GPIO_WKUP_6 pin)

Bit 2 controls GPIO_WKUP_5 (PSC6_1 pin)

Bit 3 controls GPIO_WKUP_4 (PSC6_0 pin)

Bit 4 controls GPIO_WKUP_3 (ETH_17 pin)

Bit 5 controls GPIO_WKUP_2 (PSC3_9 pin)

Bit 6 controls GPIO_WKUP_1 (PSC2_4 pin)

Bit 7 controls GPIO_WKUP_0 (PSC1_4 pin)

0 = Drive 0 on the pin (default).

1 = Drive 1 on the pin.

Note: If pin is emulating open drain, this setting results in Hi-Z

8:31 — Reserved

Loading...

Loading...