General Purpose I/O (GPIO)

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 7-41

7.3.2.1.9 GPS GPIO Simple Interrupt Enable Register—MBAR + 0x0B20

Bit Name Description

0:7 ETHR Individual bits to control the state of enabled Output Only GPIO pins.

bit 0 controls GPIO_ETHO_7 (ETH_7 pin)

bit 1 controls GPIO_ETHO_6 (ETH_6 pin)

bit 2 controls GPIO_ETHO_5 (ETH_5 pin)

bit 3 controls GPIO_ETHO_4 (ETH_4 pin)

bit 4 controls GPIO_ETHO_3 (ETH_3 pin)

bit 5 controls GPIO_ETHO_2 (ETH_2 pin)

bit 6 controls GPIO_ETHO_1 (ETH_1 pin)

bit 7 controls GPIO_ETHO_0 (ETH_0 pin)

0 = Drive 0 on the pin (default)

1 = Drive 1 on the pin

8 :11 — Reserved

12:15 I2C Individual bits to control the state of enabled Output Only GPIO pins — all reside on the

I2C ports.

bit 12 controls I2C2_CLK (I2C_2 pin)

bit 13 controls I2C2_IO (I2C_3 pin)

bit 14 controls I2C1_CLK (I2C_0 pin)

bit 15 controls I2C1_IO (I2C_1 pin)

0 = Drive 0 on the pin (default)

1 = Drive 1 on the pin

This bits can be used to toggle the clock (SCL) and data (SDA) lines of the I2C interface.

16:31 —

Reserved

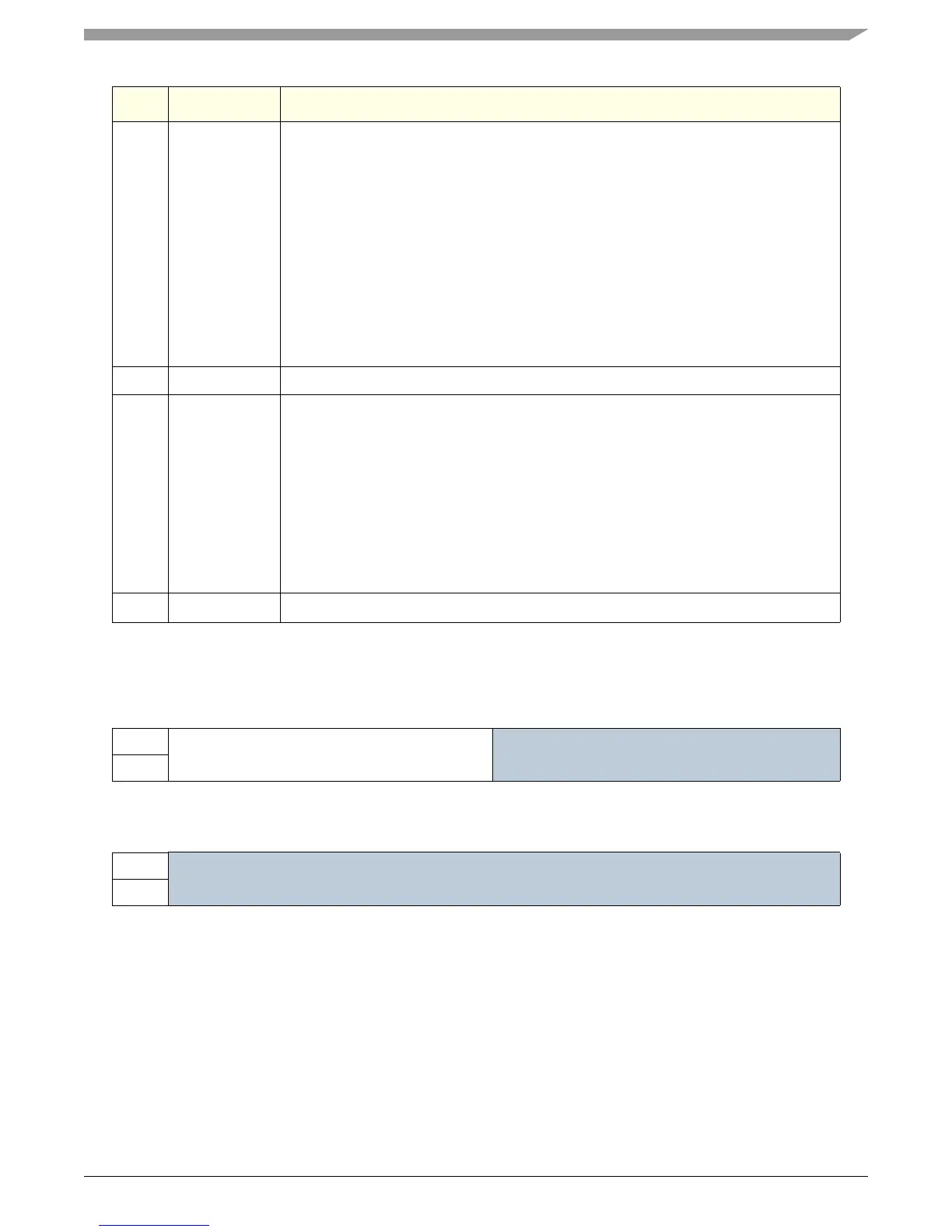

Table 7-29. GPS GPIO Simple Interrupt Enables Register

msb 012345678 9 101112131415

RSIGPIOe

Reserved

W

RESET:0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Reserved

W

RESET:0 00000000 0 0 0 00 0 0

Loading...

Loading...