MPC5200B Users Guide, Rev. 1

5-22 Freescale Semiconductor

CDM Registers

5.5.12 PSC2 Mclock Config Register—MBAR + 0x022C

This register controls the generation of the Mclock for PSC2. Before modify the register value the divider must be disabled.

5.5.13 PSC3 Mclock Config Register—MBAR + 0x0230

This register controls the generation of the Mclock for PSC3. Before modify the register value the divider must be disabled.

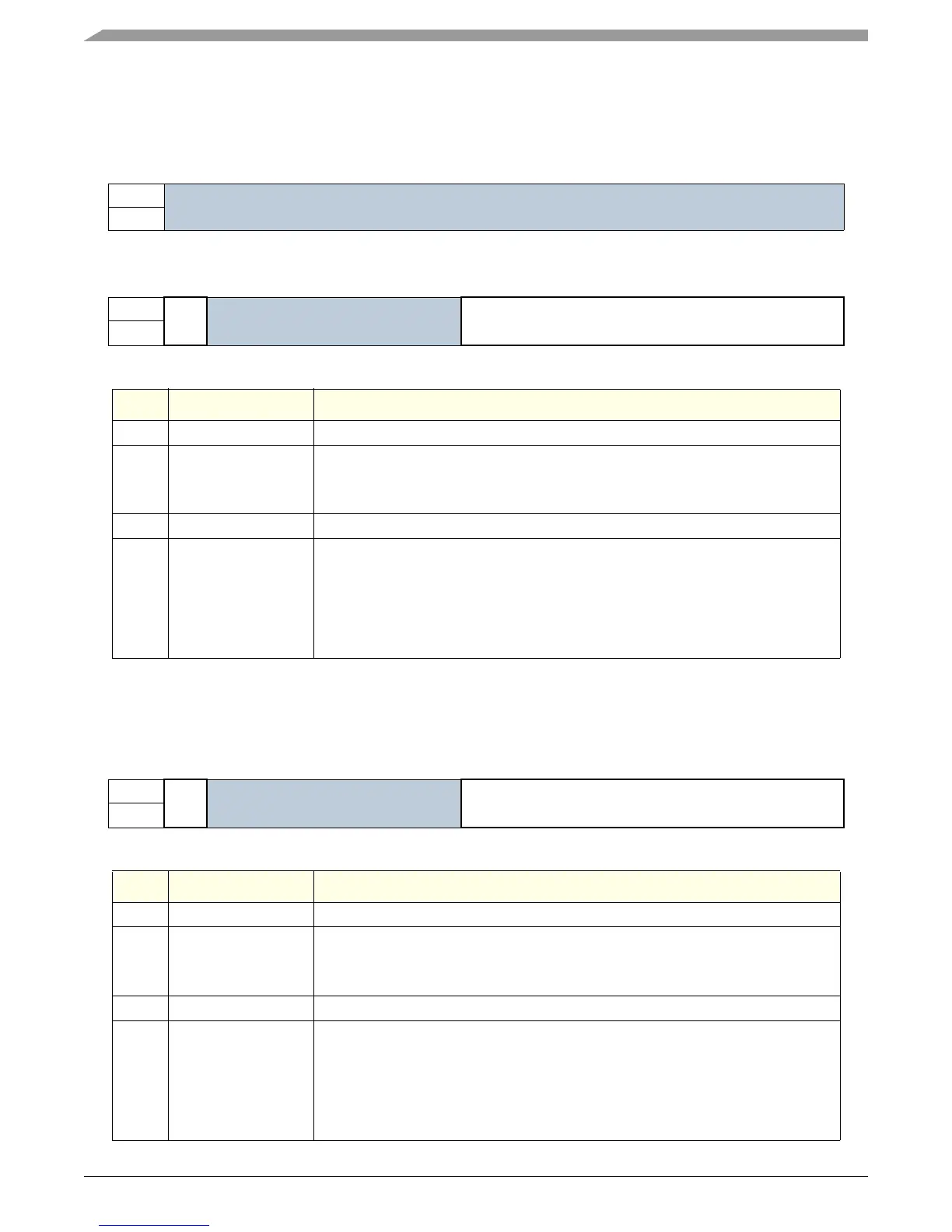

Table 5-19. CDM PSC2 Mclock Config

msb 0123456789101112131415

R Reserved

Write 0

W

RESET: 0 0 0 0000—0000000—

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Mclock

Enable

Reserved

Write 0

MclkDiv[8:0]

W

RESET: 1 0 0 0000000001111

Bit Name Description

0–15 — Reserved for future use. Write 0.

16 Mclock Enable PSC2 Mclock enable.

bit=0:Turns off internally generated Mclock.

bit=1:Turns on internally generated Mclock.

17-22 — Reserved for future use. Write 0.

23-31 MclkDiv[8:0] The counter divide the f

system

frequency by MclkDiv+1. A vallue of 0x00 in this

register turns off internally generated Mclock.

For example, a value of 7 in this register, where fsystem clock is at a frequency of

528MHz would result in a Mclock rate of 528/8, or 66 MHz.

Note: f

system

clock is always 12 or 16 times the reference clock, sys_xtal_in,

depending on sys_pll_cfg_0 at reset.

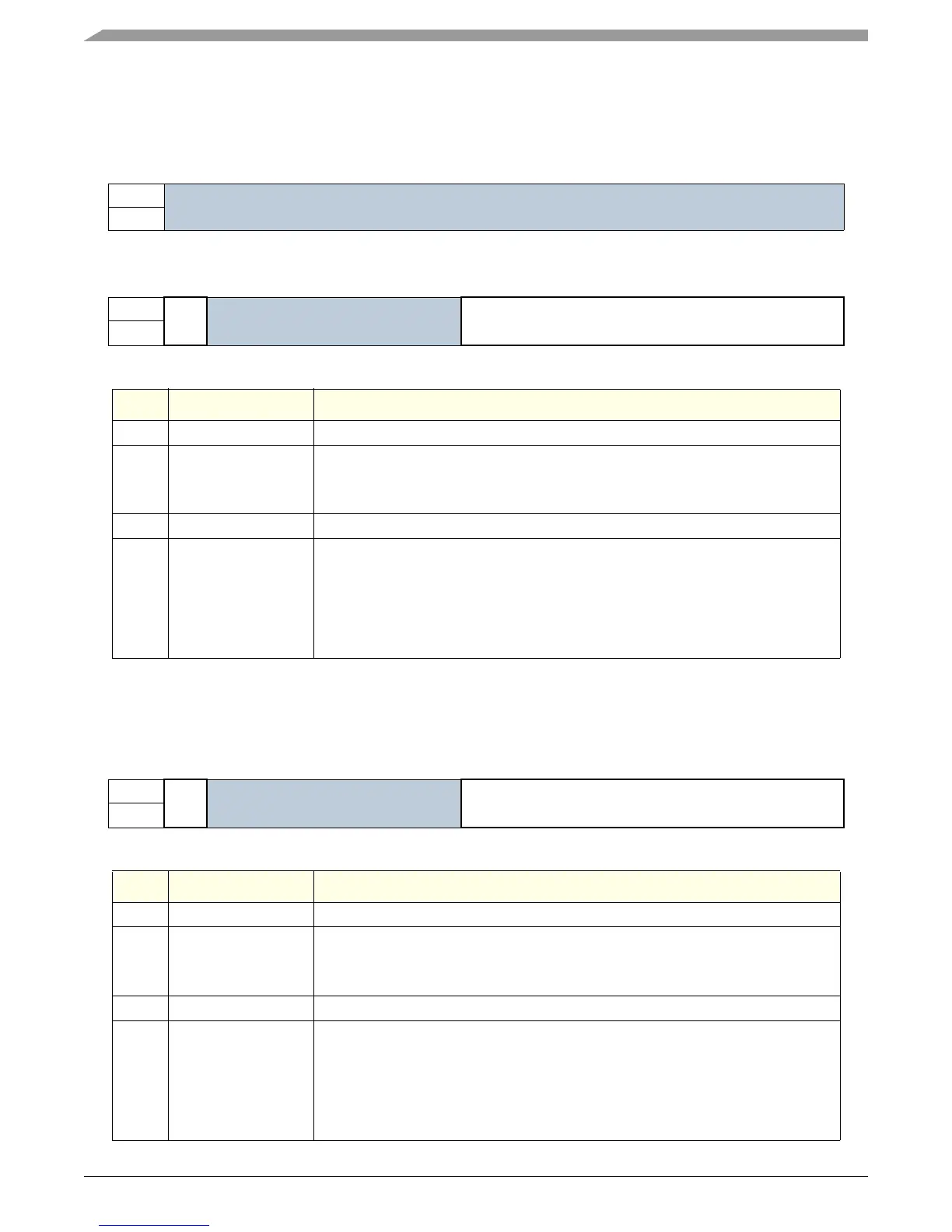

Table 5-20. CDM PSC3 Mclock Config

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Mclock

Enable

Reserved

Write 0

MclkDiv[8:0]

W

RESET: 1 0 0 0000000001111

Bit Name Description

0–15 — Reserved for future use. Write 0.

16 Mclock Enable PSC3 Mclock enable.

bit=0:Turns off internally generated Mclock.

bit=1:Turns on internally generated Mclock.

17-22 — Reserved for future use. Write 0.

23-31 MclkDiv[8:0] The counter divide the f

system

frequency by MclkDiv+1. A vallue of 0x00 in this

register turns off internally generated Mclock.

For example, a value of 7 in this register, where fsystem clock is at a frequency of

528MHz would result in a Mclock rate of 528/8, or 66 MHz.

Note: f

system

clock is always 12 or 16 times the reference clock, sys_xtal_in,

depending on sys_pll_cfg_0 at reset.

Loading...

Loading...