LocalPlus Bus (External Bus Interface)

Notes

MPC5200B Users Guide, Rev. 1

9-26 Freescale Semiconductor

9.7.2.5 SCLPC Bytes Done Status Register—MBAR + 0x3C14

Note: X: Bit does not reset to a defined value.

22 AIE Abort Interrupt Enable. If set, and a fifo error occurs during packet transmission, a cpu

interrupt from SCLPC will be generated. In any case, the Packet will be terminated

and an Abort Status bit will be set.

Note: This bit does *not* affect the Requestor to BestComm in any way.

23 NIE Normal Interrupt Enable. This bit, if set enables a cpu interrupt to occur at the end of

a normally terminated Packet. There is also a NT status bit which sets in any case.

Note: This bit does *not* affect the Requestor to BestComm in any way.

24:30 — Reserved

31 ME Master Enable. This bit must be set to 1 to allow a Restart to be generated to the

SCLPC state machine. Restart is achieved by writing 1 to Byte 0 of the Packet_Size

register. This ME bit must also be set for a Restart to occur.

Note: ME being low (inactive) will also clear Interrupt and Interrupt status. But it does

*NOT* affect the BestComm Requestor.

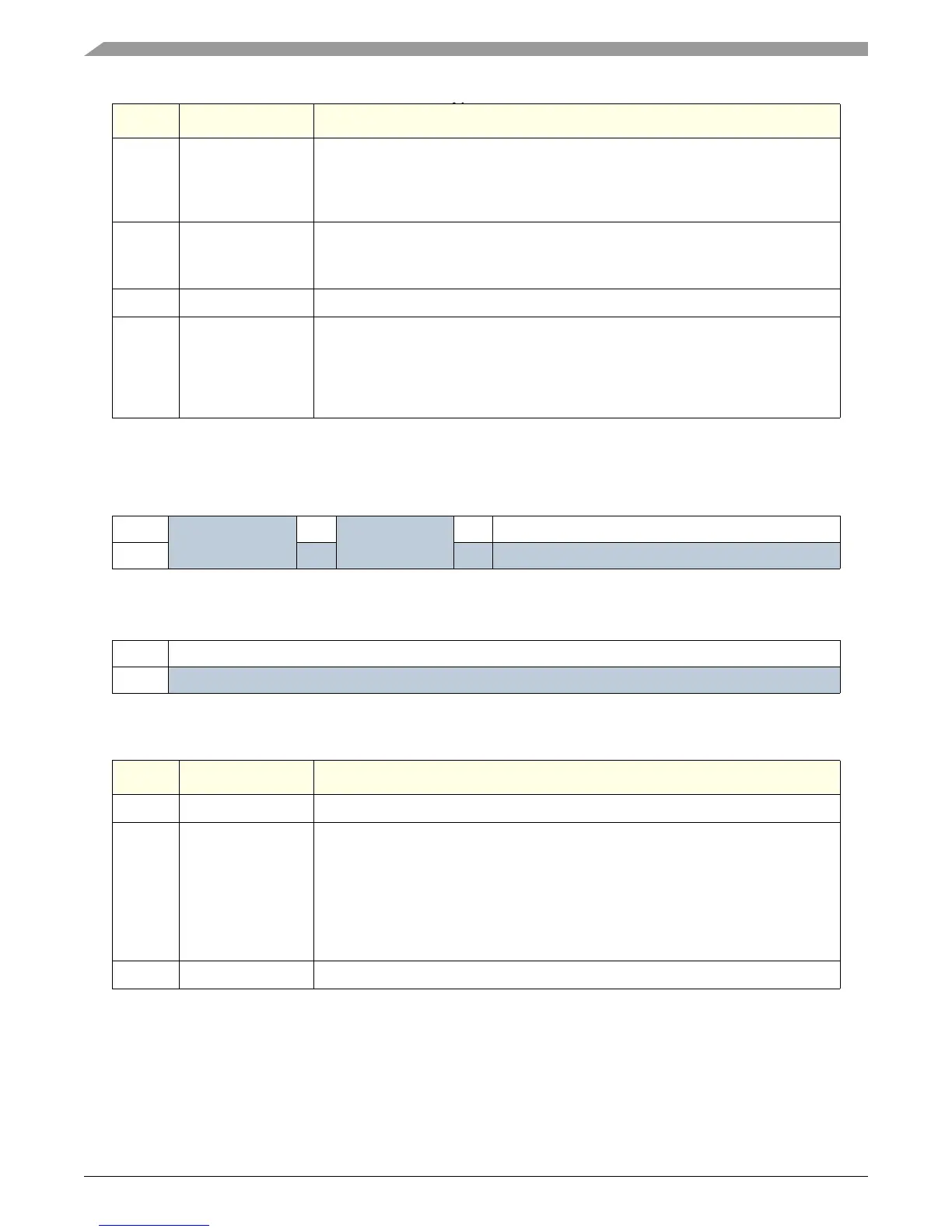

Table 9-17. SCLPC Bytes Done Status Register

msb 012345678 9 1011121314 15

R

Reserved AT Reserved NT Bytes Done

W

rwc rwc Read Only

RESET:0 0000000XX X XXXX X

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R Bytes Done

W

Read Only

RESET:X XXXXXXXX X X X XX X X

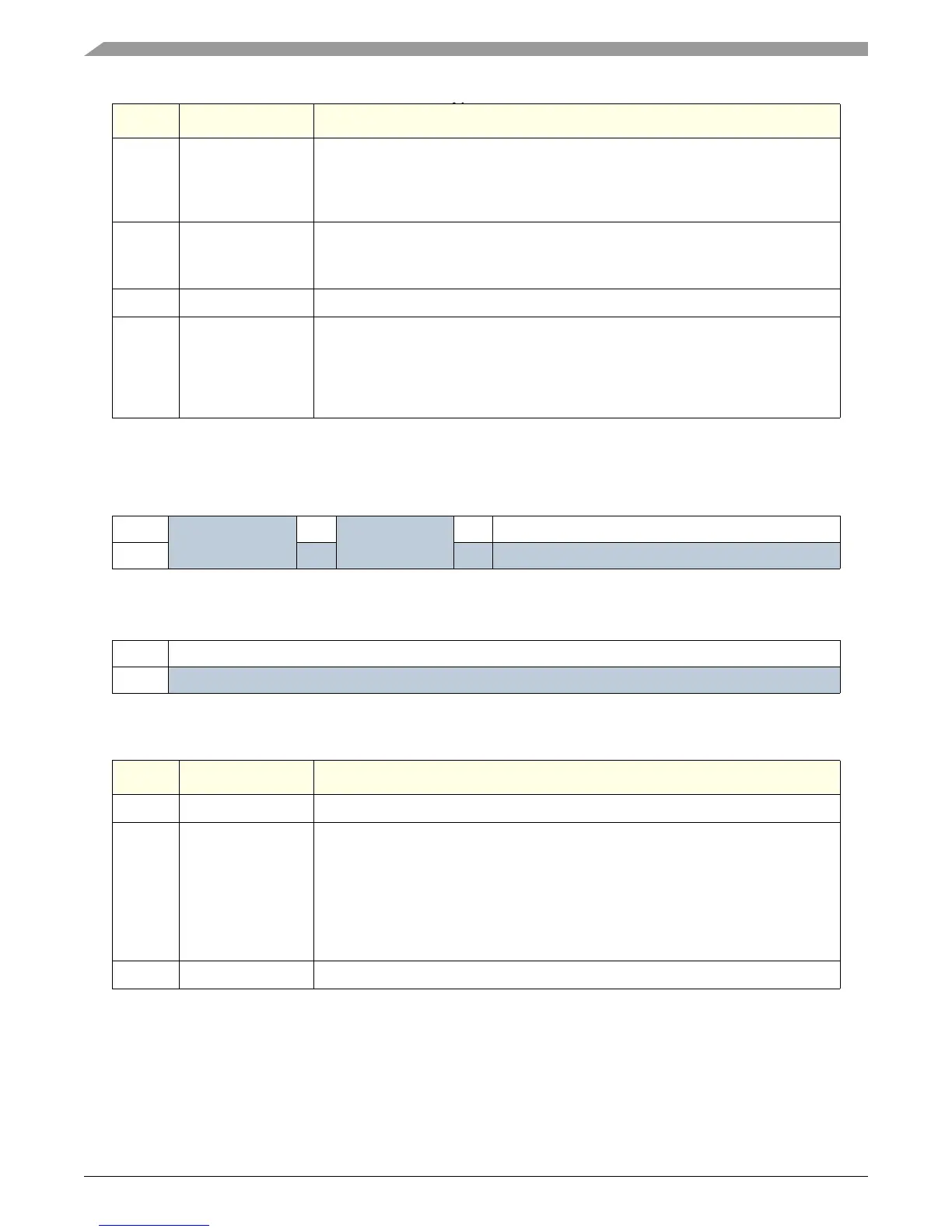

Bits Name Description

0:2 — Reserved

3 AT Abort Termination. This bit will be set to 1 if the Packet has terminated abnormally

(which is only possible if a fifoError occurred).

Note: This bit is ANDed with the AIE bit above to generate a single CPU interrupt

signal to the core. This bit is "sticky write to 1" for clearing the bit and clearing the

interrupt.

Note: This bit (and any interrupt) is also cleared if; 1) RC bit is set, 2) ME bit is clear,

or 3) Restart occurs.

4:6 — Reserved

Bits Name Description

Loading...

Loading...