MPC5200B Users Guide, Rev. 1

8-30 Freescale Semiconductor

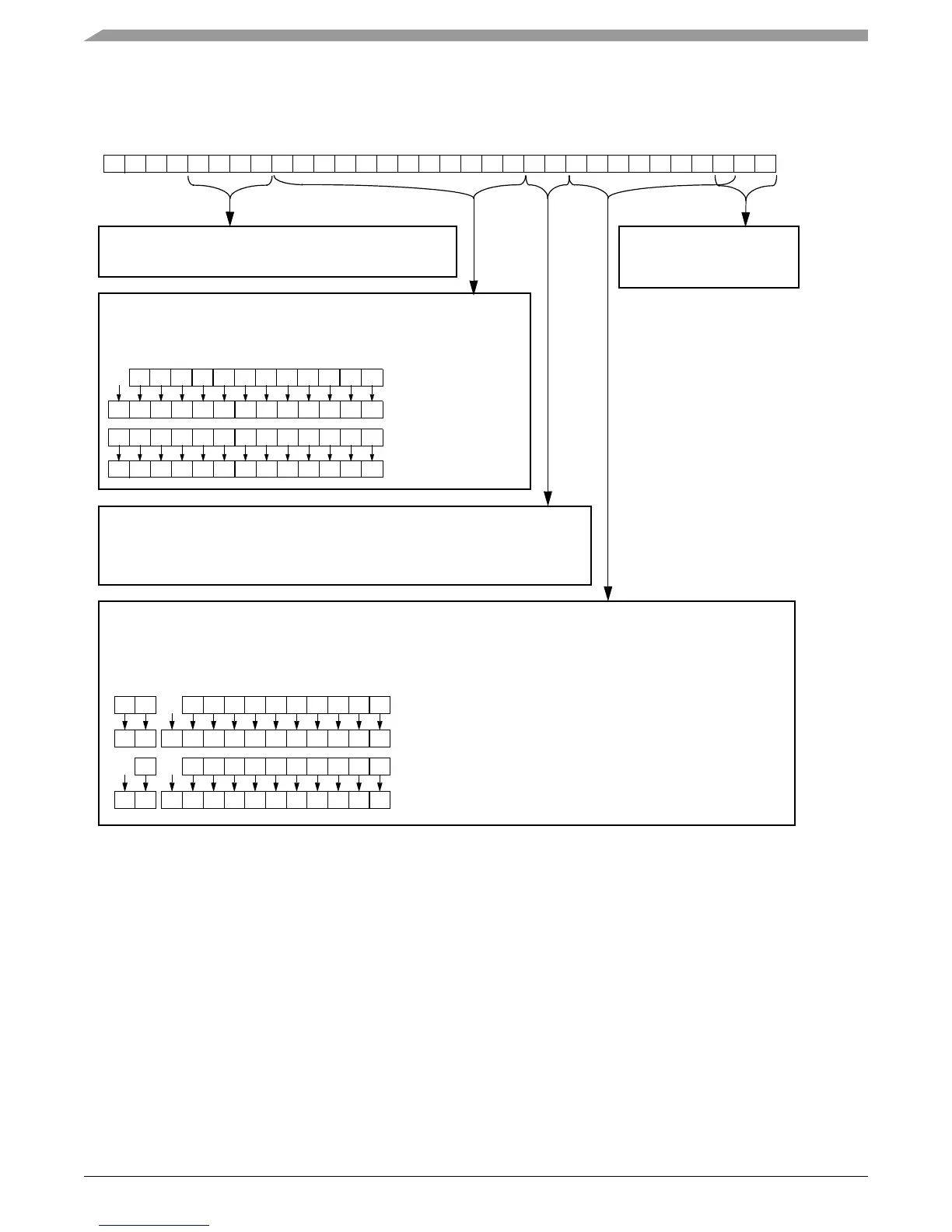

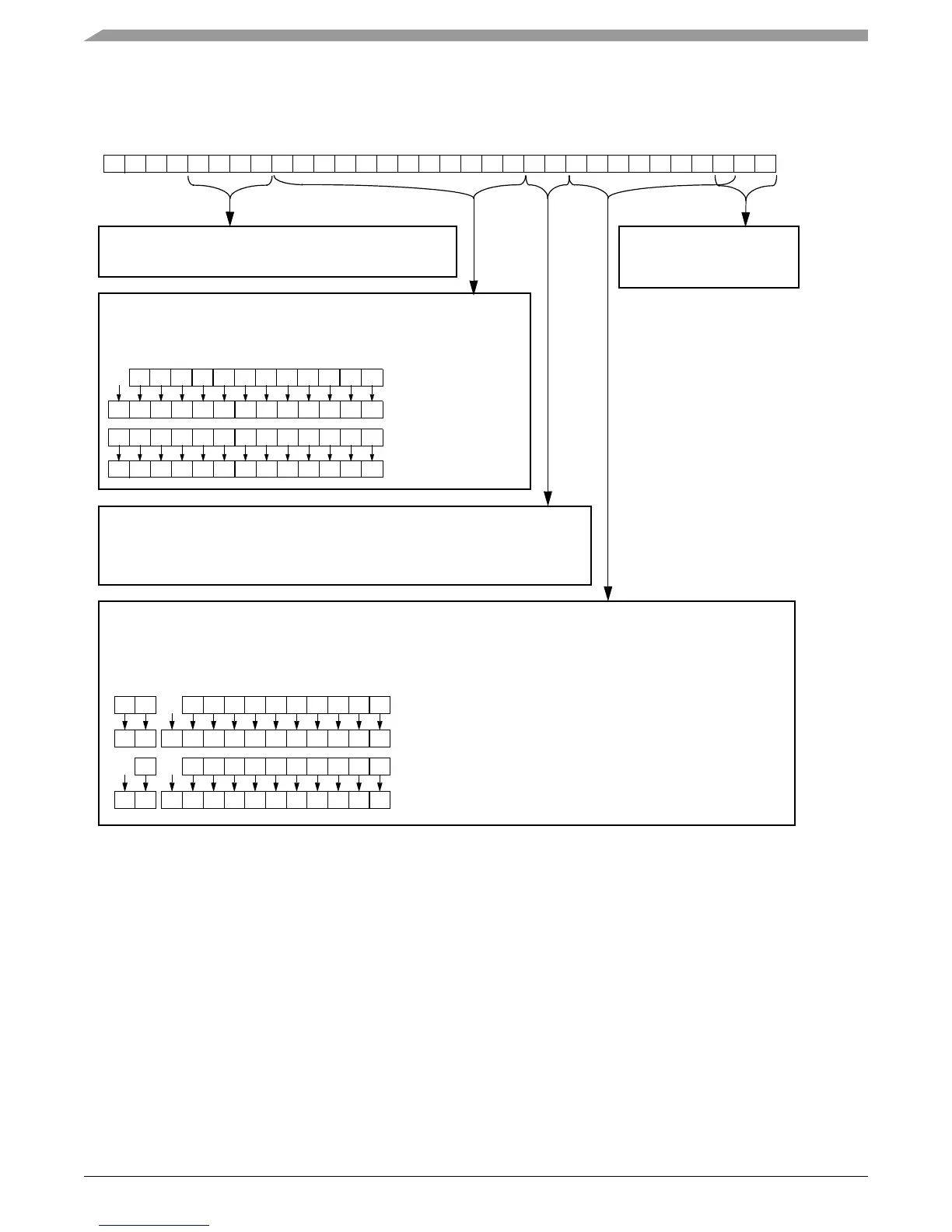

Address Bus Mapping

8.8 Address Bus Mapping

Figure 8-4. Address Bus Mapping (32-Bit External Data Width)

The Memory Controller extracts the Column Address from the XL bus address. The Column Address is presented on the

MPC5200B MEM_MA[12:0] pins during SDRAM Read and Write commands.

Column Address bits 12:8 depend on the Control register hi_addr bits. Auto Precharge (MEM_MA[10])is always inhibited

(0).

012345678910111213141516171819202122232425262728293031

Internal XL address bus

Ext MEM_MA pins, row

External MEM_MA pins, column

Internal XL address bus

XL bus address bits 29:31

control the data mask pins,

MEM_DQM[3:0].

This is an illustration of how the XL bus address enters the Memory Controller and is broken down into Row, Column, and

Bank Address fields. Shown below is the 32-bit XL bus address. The Memory Controller uses bits 4:31.

Can be used as most significant row or column address bits:

{CA12, CA11, CA9, CA8} or {CA11, CA9, CA8, RA12}

The Memory Controller extracts the Row Address from the XL bus address.

The Row Address is presented on the MPC5200B MEM_MA[12:0] pins dur-

ing SDRAM Active commands.

Row Address bit 12 depends on the Control register hi_addr bit.

1211109876543210

0 8 9 10 11 12 13 14 15 16 17 18 19

1211109876543210

5 0 6 7 22 23 24 25 26 27 28 29

Internal XL address bus

Ext MEM_MA pins, row

12 11 10 9

8

76543210

7 8 9 10 11 12 13 14 15 16 17 18 19

hi_addr = 0

hi_addr = 1

4

hi_addr = 0

11

External MEM_MA pins, column

Internal XL address bus

1211109876543210

4 0 5 6 22 23 24 25 26 27 28 290

hi_addr = 1

11

8

hi_addr = 1

17

XL bus address bits 20:21 select the internal bank of an SDRAM device. Each SDRAM

device has 4 internal banks.

XL bus address bits 20:21 are presented on the MPC5200B MEM_BA[1:0] pins during

SDRAM Active, Read, and Write commands.

Loading...

Loading...