Real-Time Clock

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 7-73

7.6.3.9 RTC Test Register/Divides Register—MBAR + 0x0820

This register is used during manufacturing test to expedite RTC testing and is not intended to be a user register. However, no protection from

software access is provided.

16:22 — Reserved

23 Int_min Periodic interrupt at each minute rollover. High indicates interrupt has occurred.

Cleared by writing 1 to this bit position.

24:30 — Reserved

31 Int_sec Periodic interrupt at each second rollover. High indicates interrupt has occurred.

Cleared by writing 1 to this bit position.

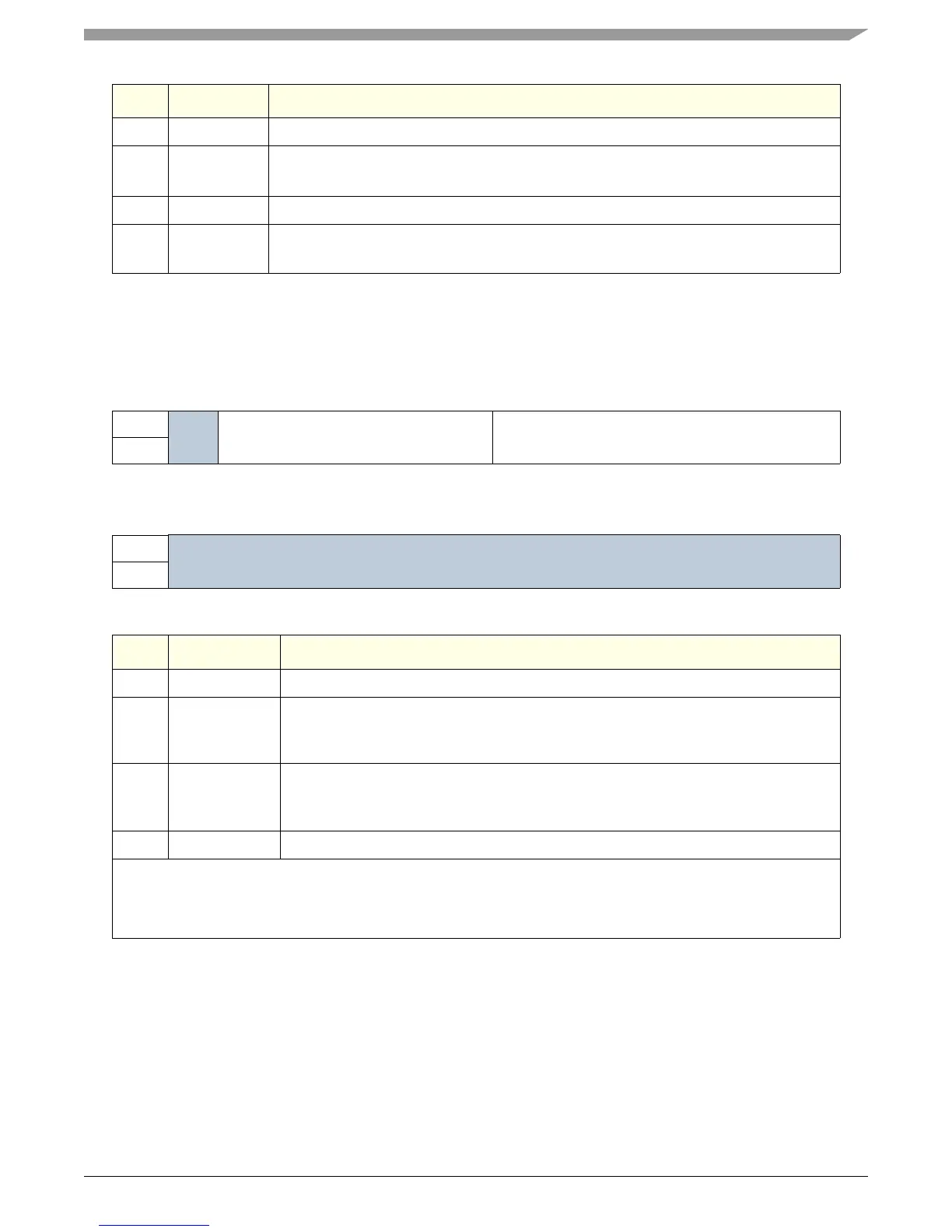

Table 7-64. RTC Test Register/Divides Register

msb 012345678 9 101112131415

R

Rsvd PTERM ETERM

W

RESET:1 11111111 1 1 1 11 1 1

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Reserved

W

RESET:0 00000000 0 0 0 00 0 0

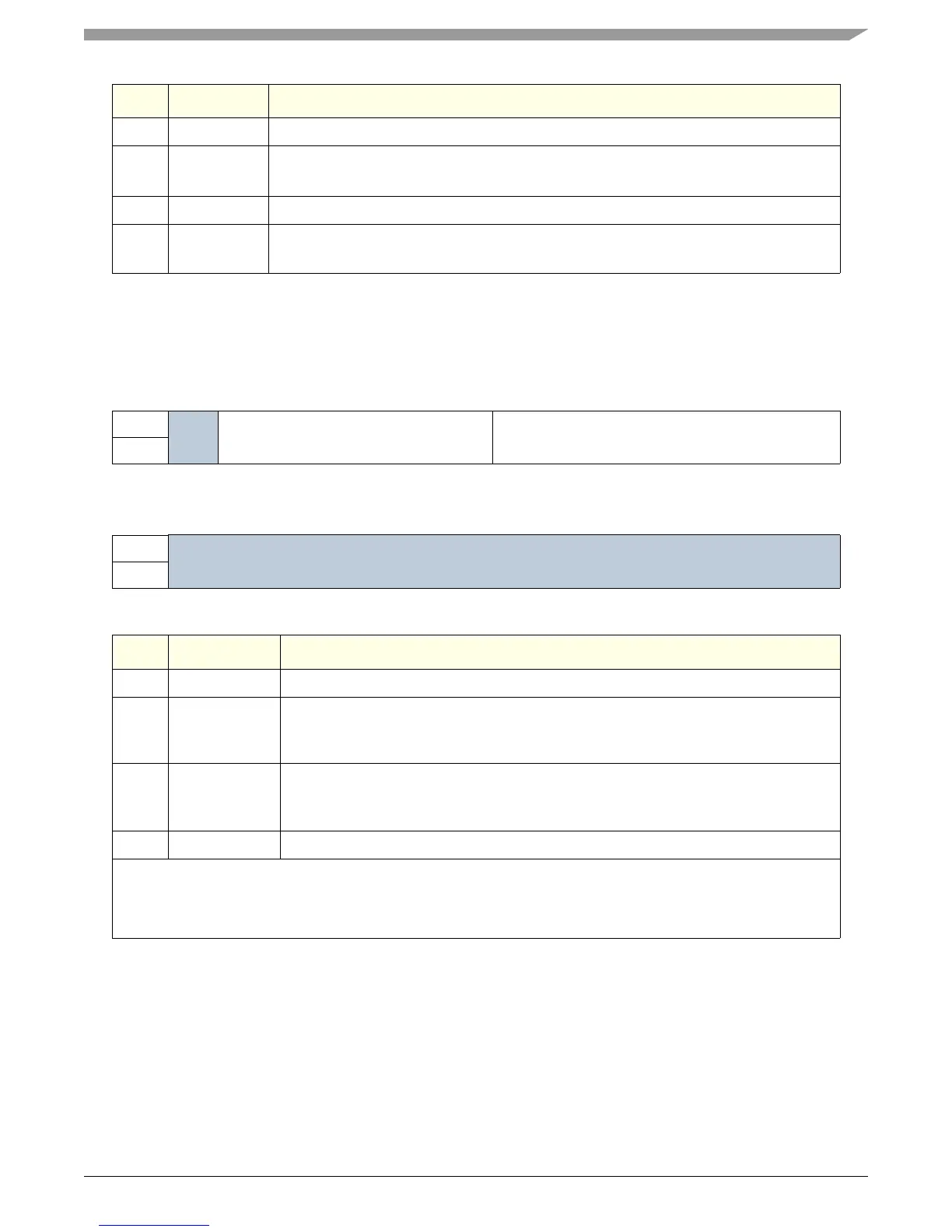

Bit Name Description

0—Reserved

1:7 PTERM Prescale Termination value, the number of 32KHz clocks per 7-bit prescale counter.

Default at reset is the maximum (and proper) value of 128 decimal. Any value lower than

this causes the RTC to run fast.

8:15 ETERM External Termination value, the number of prescaled counts per 8-bit external counter.

Default at reset is the maximum (and proper) value of 256 decimal. Any value lower than

this causes the RTC to run fast.

16:31 — Reserved

Note: The 32.768KHz crystal frequency is divided by PTERM, which is then divided by ETERM to produce a 1 second

time interval. It is conceivable that a system might wish to adjust these values to produce a more locally accurate clock

rate. However, be aware that these values are affected by reset. Therefore, any adjustment value must be stored and

retrieved from non-volatile memory. Further, the adjustment could only increase the clock rate, not decrease it.

Bits Name Description

Loading...

Loading...