MPC5200B Users Guide, Rev. 1

10-8 Freescale Semiconductor

Registers

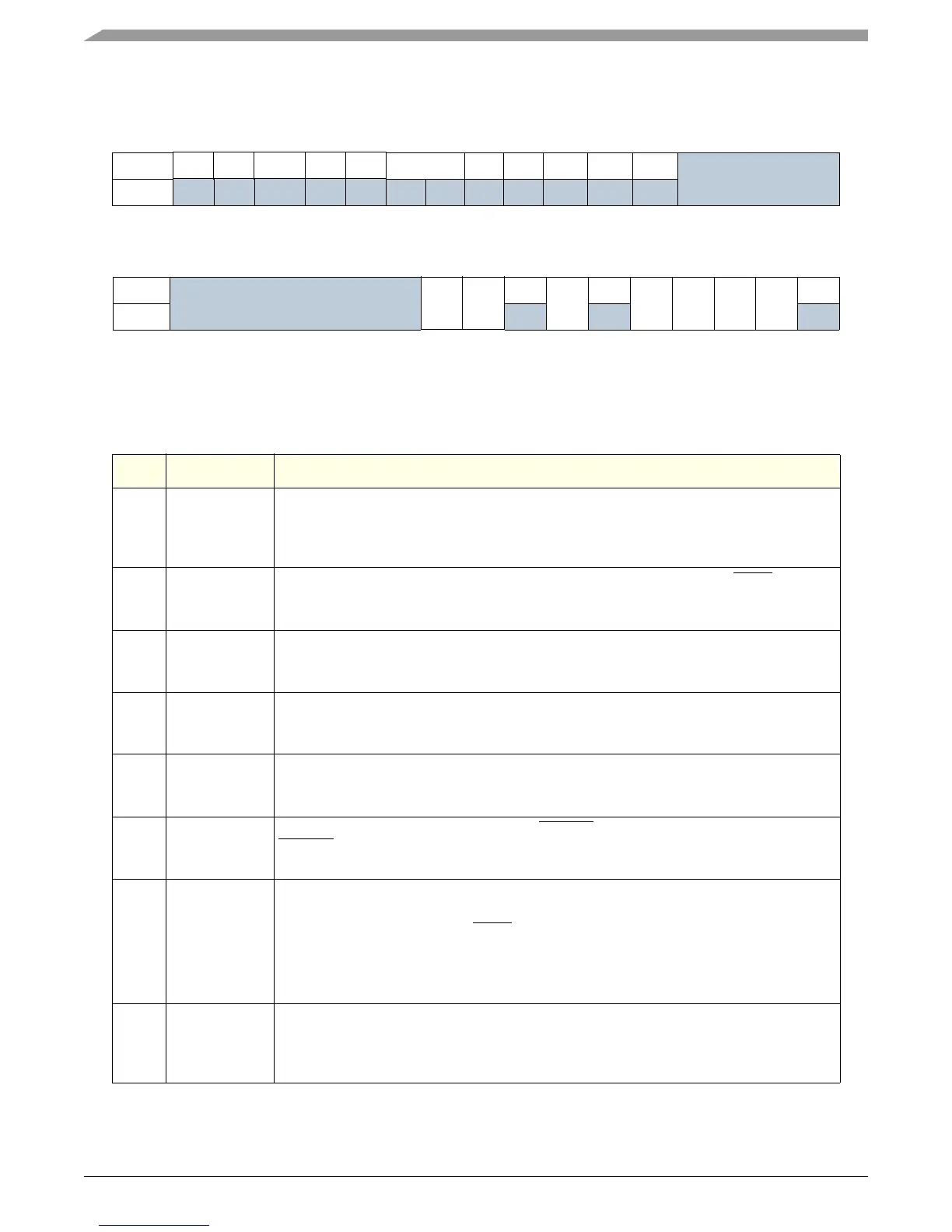

10.3.1.2 Status/Command Registers PCISCR(R/RW/RWC) —MBAR + 0x0D04

Bits 31-27 and 24 are read-write-clear (RWC).

• Hardware can set RWC bits, but cannot clear them.

• Only PCI configuration cycles can clear RWC bits that are currently set by writing a 1 to the bit location. Writing a 1 to a RWC bit

that is currently a 0 or writing a 0 to any RWC bit has no effect.

msb

0

1 2 345678 9 101112131415

R PE SE MA TR TS DT DP FC R 66M C

Reserved

W

rwc rwc rwc rwc rwc rwc

RESET:00 0 000101 0 1 0 0 000

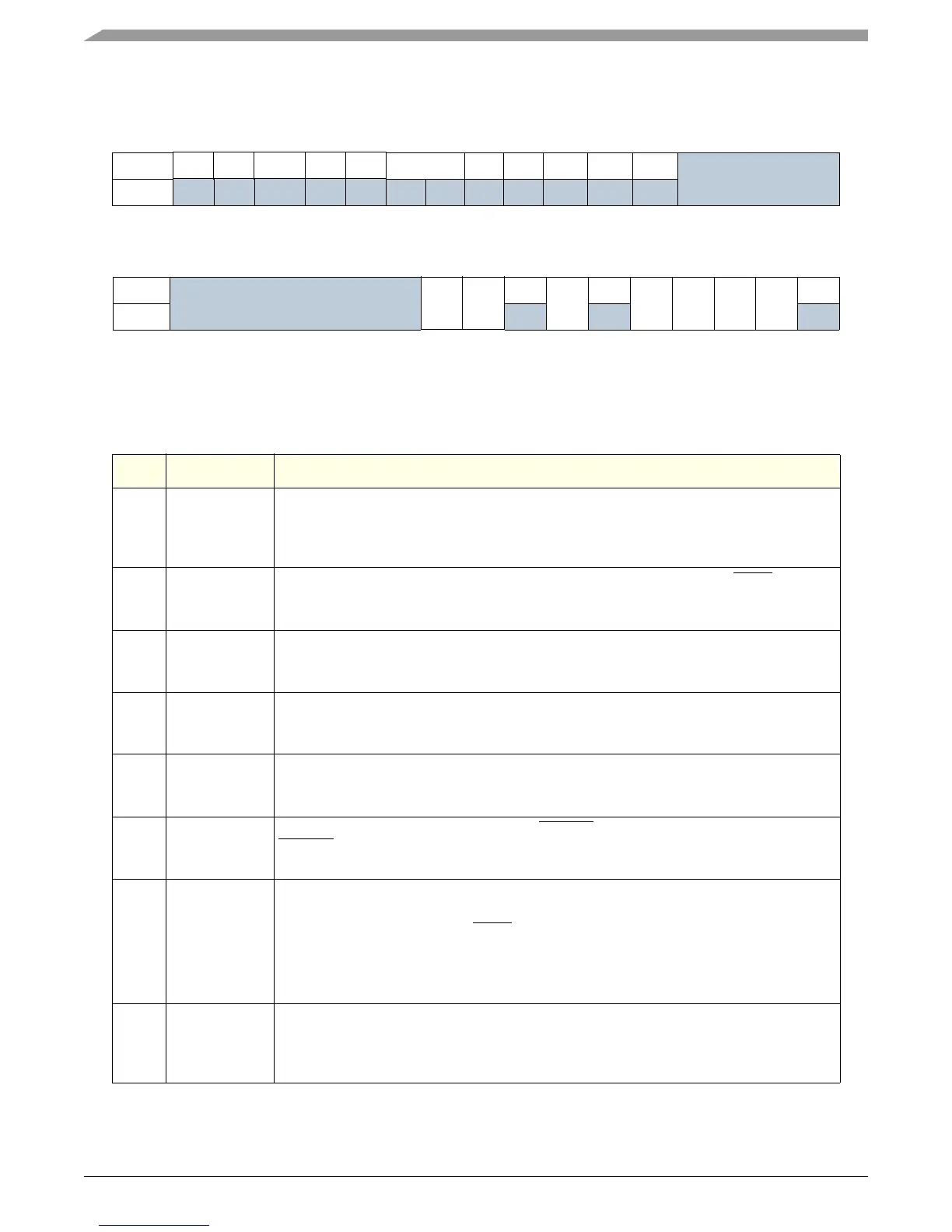

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R

Reserved F SStPERVMWSpBMIO

W

RESET:0000000000000000

Bits Name Description

0 Parity Error

Detected

(PE)

This bit is set when a parity error is detected, even if the Parity Error Response bit in the

Command Register (bit 6) is disabled. A CPU interrupt will be generated if the

PCIGSCR[PEE] bit is set. This register is read-write-clear (RWC) via PCI configuration

cycles.

1 System Error

Signalled

(SE)

This bit is set whenever MPC5200B generates a PCI System Error on the SERR

line. This

register is read-write-clear (RWC) via PCI configuration cycles.

2Master Abort

Received

(MA)

This bit is set whenever MPC5200B is the PCI master and terminates a transaction (except

for Special Cycle) with a Master-Abort. This register is read-write-clear (RWC) via PCI

configuration cycles.

3 Target Abort

Received

(TR)

This bit is set whenever MPC5200B is the PCI master and a transaction is terminated by a

Target Abort from the currently-addressed target. This register is read-write-clear (RWC) via

PCI configuration cycles.

4 Target Abort

Signalled

(TS)

This bit is set whenever MPC5200B is the PCI target and it terminates a transaction with a

Target Abort. This register is read-write-clear (RWC) via PCI configuration cycles.

5:6 DEVSEL#

Timing

(DT)

Fixed to 01. These bits encode a medium DEVSEL

timing. This defines the slowest

DEVSEL

timing when MPC5200B is the PCI target (except configuration accesses).

7 Master Data

Parity

Error

(DP)

This bit applies only when MPC5200B is PCI master and is set only if the following

conditions are met:

• MPC5200B-as-master sets PERR itself during a read or detected it asserted by the

target during a write

• The Parity Error Response bit in the Command Register, bit 6, is set to 1

This register is read-write-clear (RWC) via PCI configuration cycles.

8Fast

Back-to-Back

Capable

(FC)

Fixed to 1. The MPC5200B PCI controller does NOT support Fast Back-to-Back

transactions.

Loading...

Loading...