MPC5200B Users Guide, Rev. 1

10-24 Freescale Semiconductor

Registers

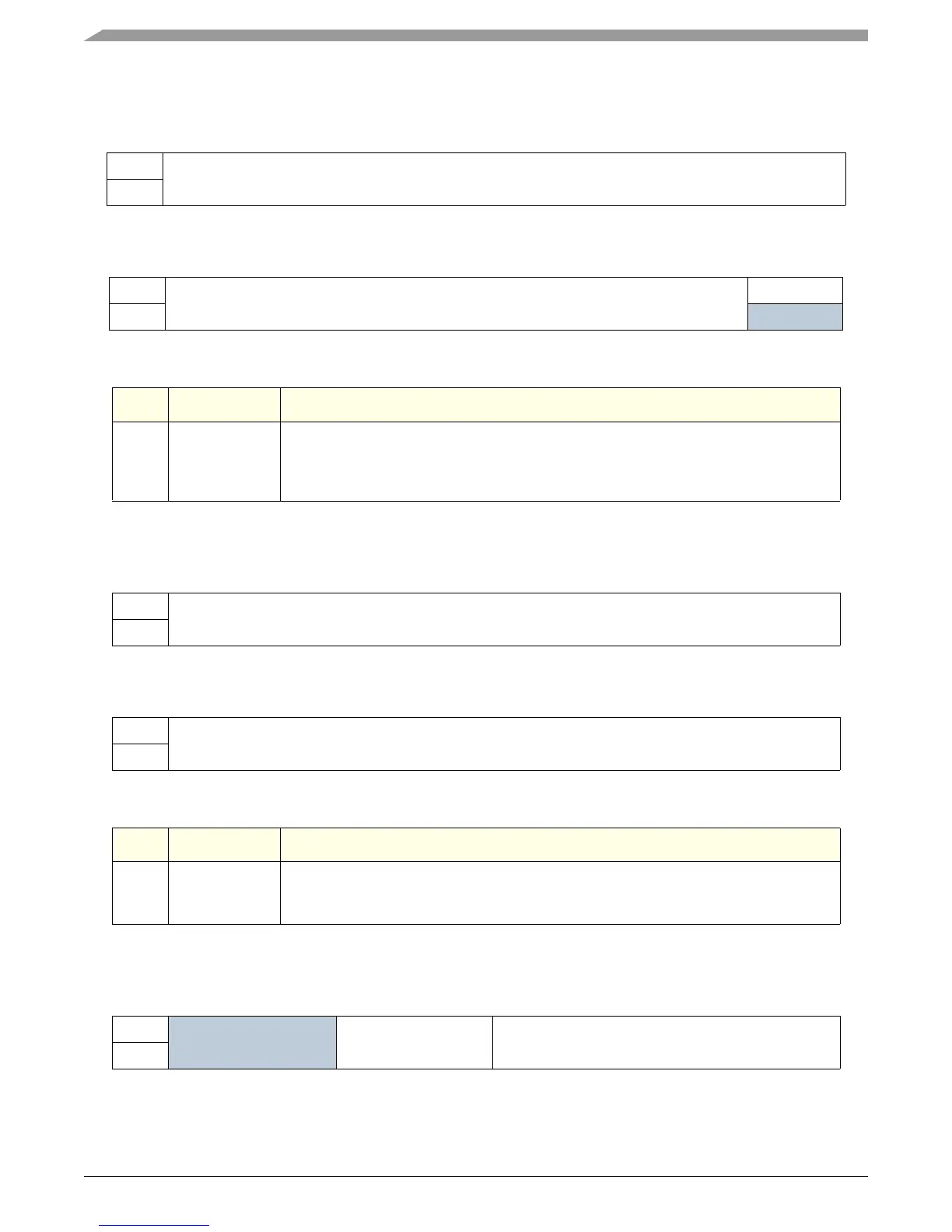

10.3.3.1.1 Tx Packet Size PCITPSR(RW) —MBAR + 0x3800

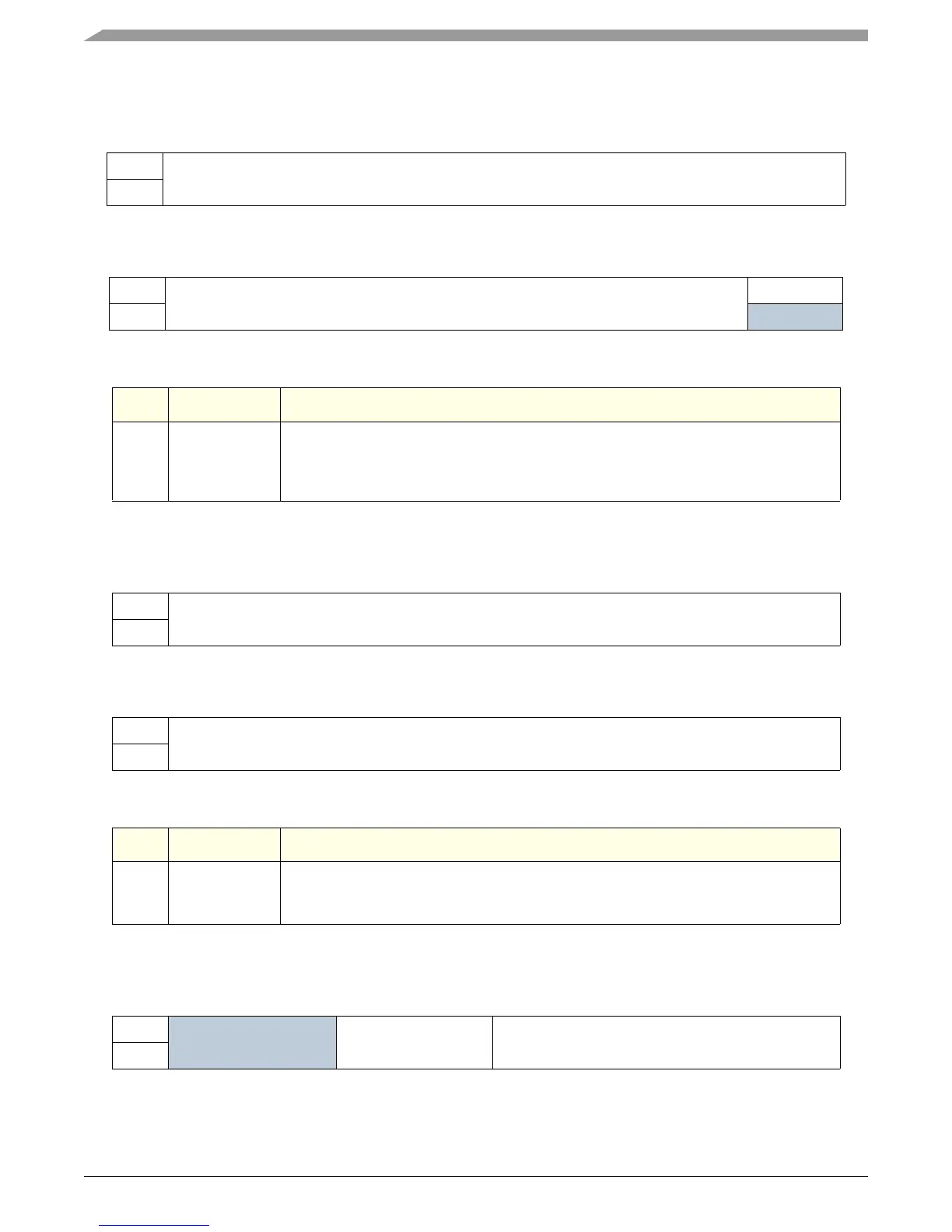

10.3.3.1.2 Tx Start Address PCITSAR(RW) —MBAR + 0x3804

10.3.3.1.3 Tx Transaction Control Register PCITTCR(RW) —MBAR + 0x3808

msb 012345678 9 10111213 14 15

R Packet_Size[31:16]

W

RESET 0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R Packet_Size[15:2] PacketSize[1:0]

W

RESET 0 00000000 0 0 0 00 0 0

Bits Name Description

0:31 Packet_Size User writes the number of bytes for transmit controller to send over PCI.The two low bits

are hardwired low; only 32-bit data transfers to the FIFO are allowed. Writing to this register

also completes a Restart Sequence as long as the Master Enable bit, PCITER[ME], is high

and Reset Controller bit, PCITER[RC], is low.

msb 012345678 9 1011121314 15

R Start_Add

W

RESET 0 00000000 0 0 0 00 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb

R Start_Add

W

RESET 0 00000000 0 0 0 00 0 0

Bits Name Description

0:31 Start_Add User writes the PCI address to be presented for the first DWORD (32 bit) of a PCI packet.

The PCI Tx controller will track and calculate the necessary address for subsequent

transactions (addressing is assumed to be sequential from the start address).

msb 012345678 9 1011121314 15

R

Reserved PCI_cmnd Max_Retries

W

RESET 0 0 0 0 0111 0 0 0 0 0 0 0 0

Loading...

Loading...