PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 15-25

The Mclk frequency is generated in the Clock Distribution Module (CDM) by dividing down the f

system

frequency as follows:

There is a separate cdm_pscX_bitclk_config register in the CDM for each of PSC1,2,3 and 6, which are the PSCs available for use in Codec

modes. These cdm_pscX_bitclk_config registers are further described in the CDM Section 5.5.11, PSC1 Mclock Config Register—MBAR +

0x0228 to Section 5.5.14, PSC6 (IrDA) Mclock Config Register—MBAR + 0x0234.

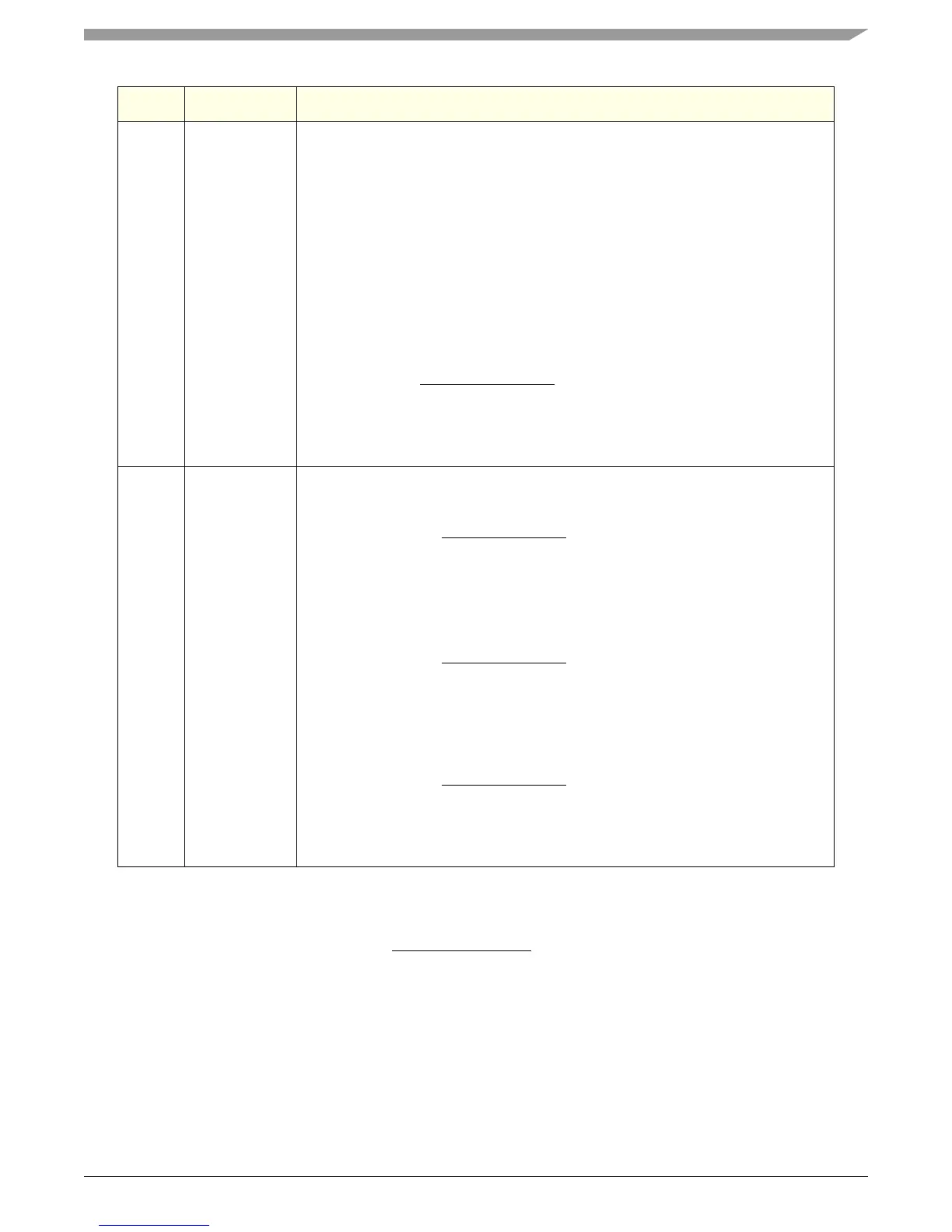

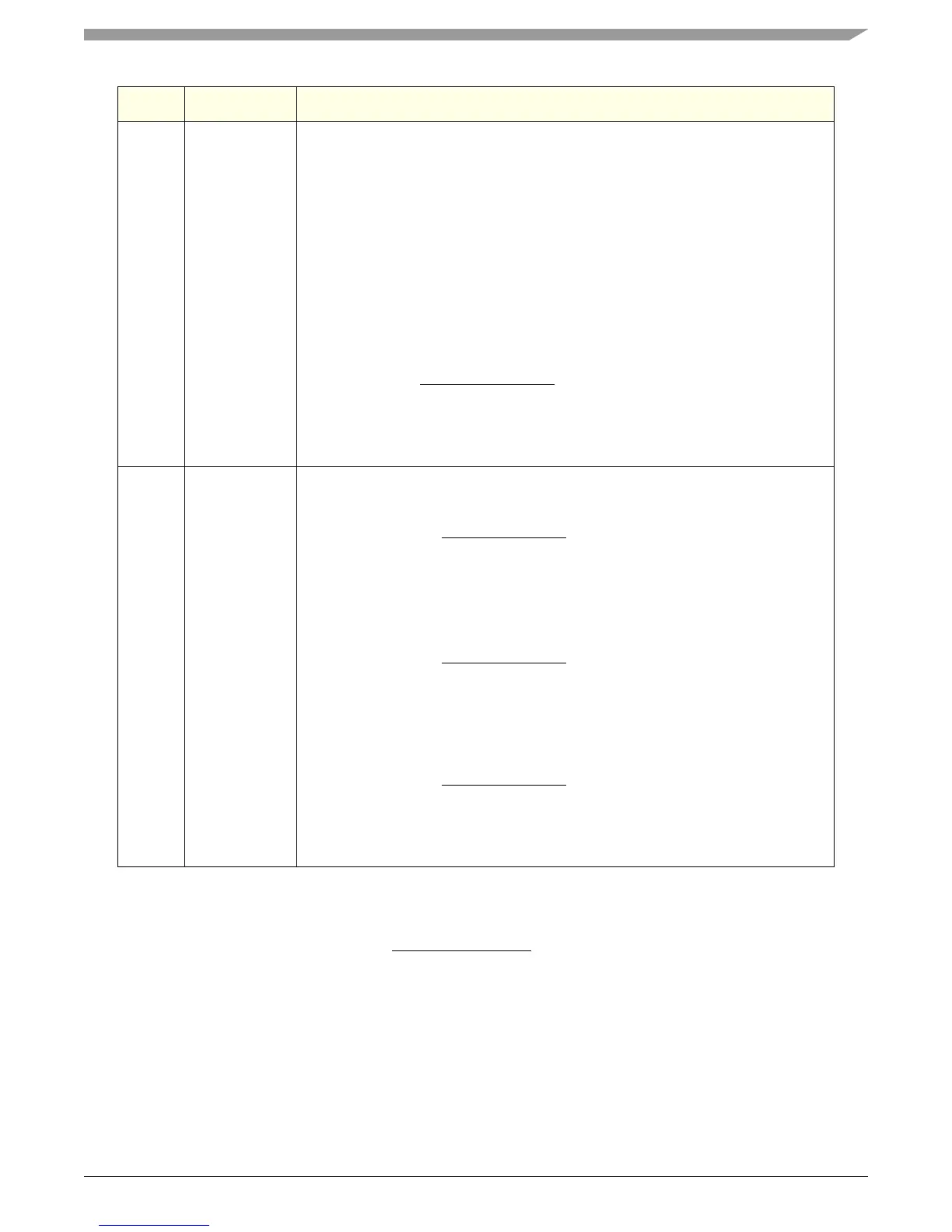

Bit Name Description

0:7 FrameSyncDiv Codec—Frame Sync Divider

FrameSync is generated internally by dividing down the Bit Clock. The FrameSyncDiv

defines the number of Bit clock cycles between two active frame edges:

FrameSync Length = FrameSyncDiv[0:7] + 1

For more information see also Section 15.3.2.3, Transmitting and Receiving in “Soft

Modem” Codec Mode

Codec / SPI—delay before SCK (DSCKL)

When the PSC is in SPI mode (SICR[SPI] = 1), the FrameSyncDiv divider is used to

determine the length of time the PSC delays after SS goes low/active before the first

SCK transition of the serial transfer. This is a feature that exists in a QSPI. The following

equation determines the actual delay before SCK:

other Modes—Reserved

Note: The value 0x00 stops this counter and disables the clock generator.

7:23 BitClkDiv Codec—Bit Clock Divider

Bit clock is generated internally by dividing down the Mclk frequency as follows:

Codec SPI—Baud Rate

SCK is generated internally by dividing down the Mclk frequency as follows:

MIR / FIR—Irda clock

IrdaClk is generated internally by dividing down the Mclk frequency as follows:

other Modes—Reserved

Note: The value 0x00 stops this counter and disables the clock generator.

DSCKL delay =

Mclk Frequency

FrameSyncDiv[0:7] + 1)

BitClk frequency =

Mclk Frequency

BitClkDiv[0:15] + 1

SCK frequency =

Mclk Frequency

BitClkDiv[0:15] + 1

IrdaClk frequency =

Mclk Frequency

BitClkDiv[0:15] + 1

Mclk =

MclkDiv [8:0] + 1

f

system

Loading...

Loading...