PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 15-37

Bit Name Description

0:3 — Reserved

4:7 F_FDIV FIR—Clock divide ratio in FIR mode.

The bit frequency is derived by:

This bit frequency should be 8 MHz. In order to receive the minimum pulse width described in

the IrDA spec, (F_FDIV + 1) should be larger than or equal to 4. Table 15-56 shows several

frequency selection. For more informations about the frequency generation see also Figure

15-19, Section 15.2.14, Codec Clock Register (0x20)—CCR and Section 15.3.4.3, PSC in FIR Mode.

other Modes—Reserved

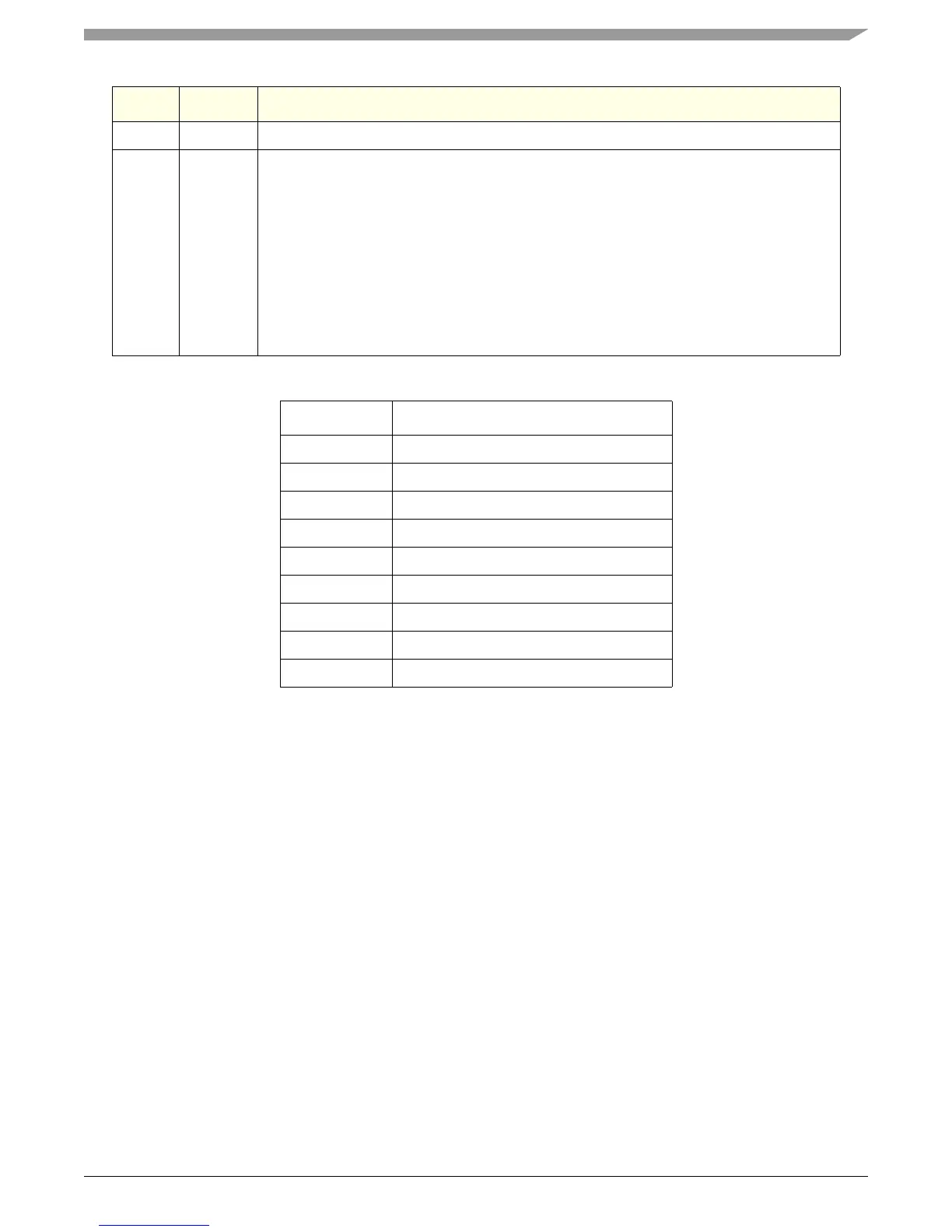

Table 15-56. Frequency Selection for FIR Mode

F_FDIV[3:0] Frequency of IrdaClk [MHz]

0x3 32.0

0x4 40.0

0x5 48.0

0x6 56.0

0x7 64.0

0x8 72.0

0x9 80.0

0xA 88.0

... ...

f

bit

f

IrdaClk

F_FDIV + 1

------------------------------

=

Loading...

Loading...