Functional Description

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor 20-21

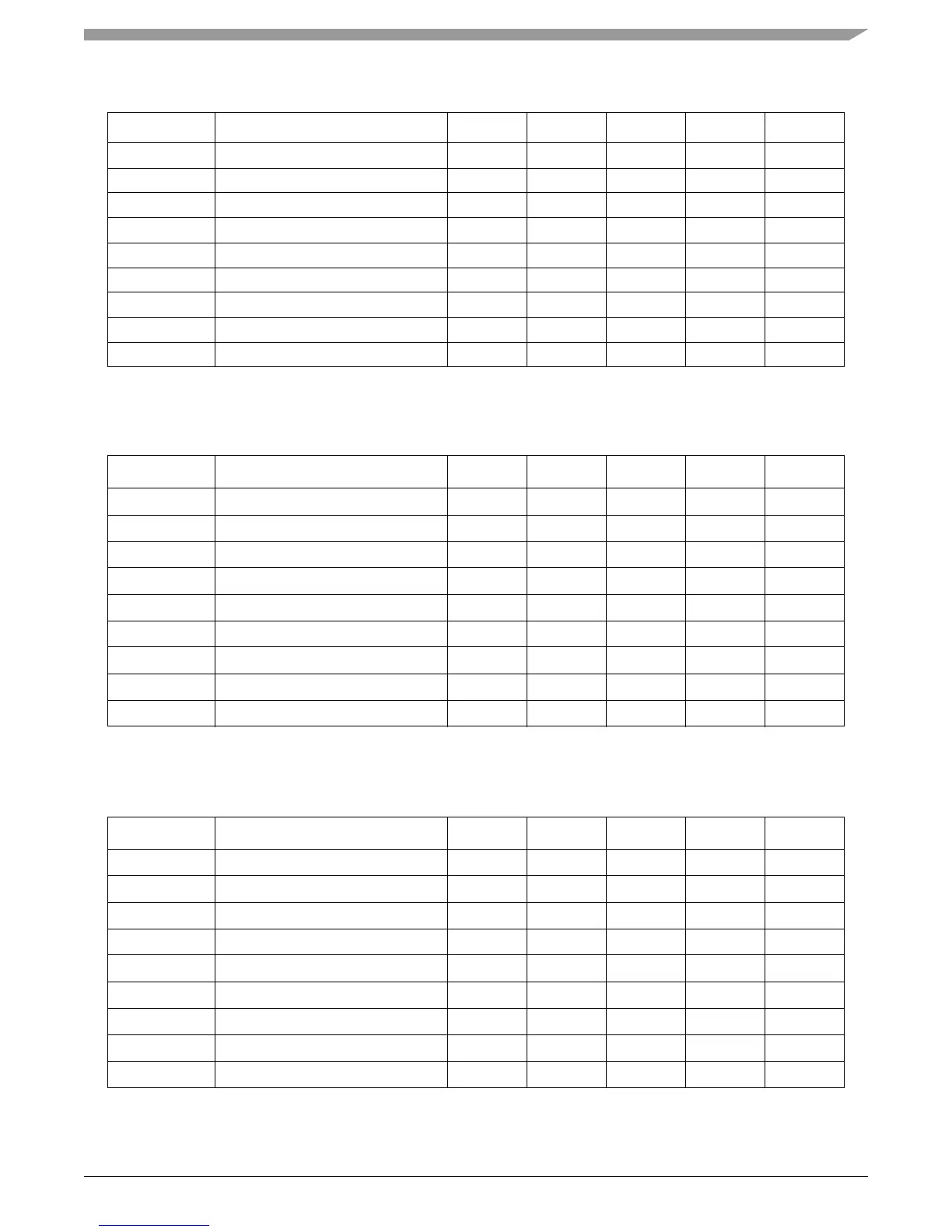

Table 20-16. BDLC Receiver VPW Symbol Timing for Binary Frequencies

Number Characteristic Symbol Min Typ Max Unit

1 Passive Logic 0 T

rvp1

34 67 100 t

bdlc

2 Passive Logic 1 T

rvp2

101 134 171 t

bdlc

3 Active Logic 0 T

rva1

101 134 171 t

bdlc

4 Active Logic 1 T

rva2

34 67 100 t

bdlc

5 Start of Frame (SOF) T

rva3

172 210 251 t

bdlc

6 End of Data (EOD) T

rvp3

172 210 251 t

bdlc

7 End of Frame (EOF) T

rv4

252 293 314 t

bdlc

8 Inter-Frame Separator (IFS) T

rv5

315 --- --- t

bdlc

9 Break Signal (BREAK) T

rv6

252 --- --- t

bdlc

Note:

1. The receiver symbol timing boundaries are subject to an uncertainty of 1 t

bdlc

due to sampling considerations.

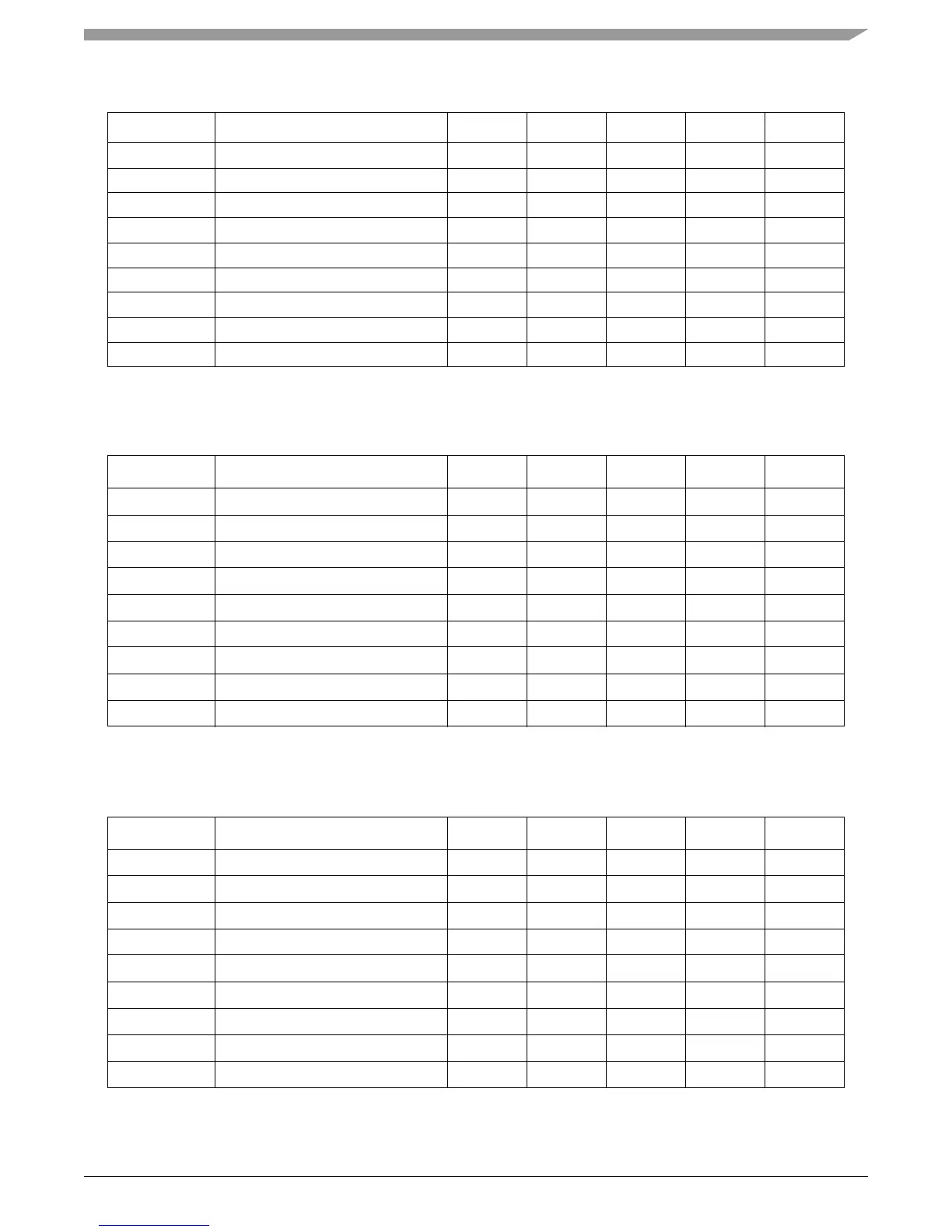

Table 20-17. BDLC Receiver VPW 4X Symbol Timing for Integer Frequencies

Number Characteristic Symbol Min Typ Max Unit

1 Passive Logic 0 T

rvp1

81623t

bdlc

2 Passive Logic 1 T

rvp2

24 32 40 t

bdlc

3 Active Logic 0 T

rva1

24 32 40 t

bdlc

4 Active Logic 1 T

rva2

81623t

bdlc

5 Start of Frame (SOF) T

rva3

41 50 59 t

bdlc

6 End of Data (EOD) T

rvp3

41 50 59 t

bdlc

7 End of Frame (EOF) T

rv4

60 70 74 t

bdlc

8 Inter-Frame Separator (IFS) T

rv5

75 --- --- t

bdlc

9 Break Signal (BREAK) T

rv6

60 --- --- t

bdlc

Note:

1. The receiver symbol timing boundaries are subject to an uncertainty of 1 t

bdlc

due to sampling considerations.

Table 20-18. BDLC Receiver VPW 4X Symbol Timing for Binary Frequencies

Number Characteristic Symbol Min Typ Max Unit

1 Passive Logic 0 T

rvp1

91725t

bdlc

2 Passive Logic 1 T

rvp2

26 34 42 t

bdlc

3 Active Logic 0 T

rva1

26 34 42 t

bdlc

4 Active Logic 1 T

rva2

91725t

bdlc

5 Start of Frame (SOF) T

rva3

43 53 62 t

bdlc

6 End of Data (EOD) T

rvp3

43 53 62 t

bdlc

7 End of Frame (EOF) T

rv4

63 74 78 t

bdlc

8 Inter-Frame Separator (IFS) T

rv5

79 --- --- t

bdlc

9

Break Signal (BREAK) T

rv6

63 --- --- t

bdlc

Note:

1. The receiver symbol timing boundaries are subject to an uncertainty of 1 t

bdlc

due to sampling considerations.

Loading...

Loading...