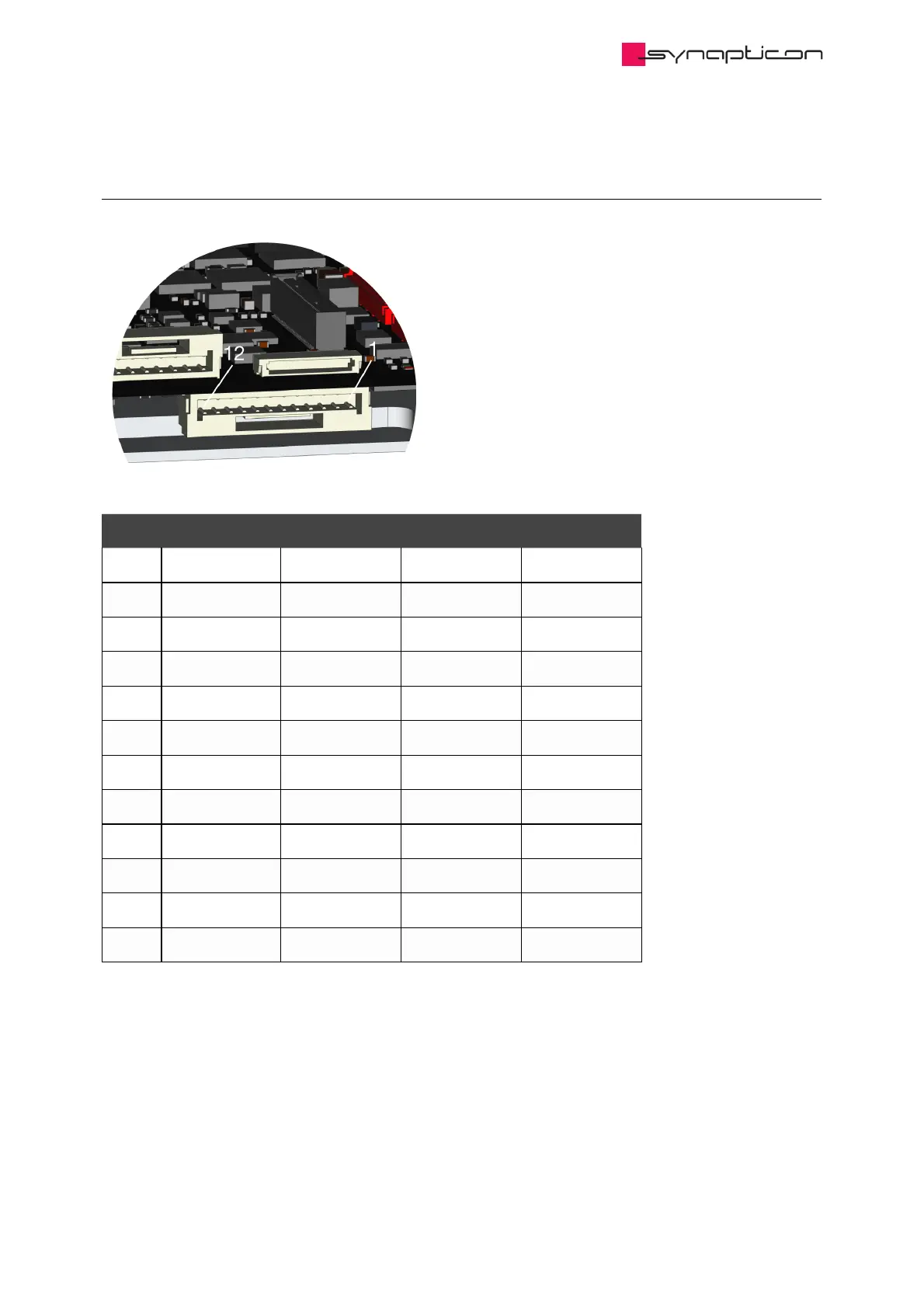

1.5.4.3.2.5 Encoder Port 3 / Digital IO

Pin # GPIO REM 14/16MT BiSS (LVTTL) SSI (LVTTL)

1 3.3 V 3.3 V 3.3 V 3.3 V

2 Digital IO 1 SS SLO Data

3 Digital IO 2 SCK MA Clock

4 Ground Ground Ground Ground

5 Digital IO 3 MISO – –

6 Digital IO 4 MOSI – –

7 5 V 5 V 5 V 5 V

8 – – – –

9 Digital IO 5 – – –

10 Digital IO 6 – – –

11 – – – –

12 – – – –

All Digital IOs are 3.3 V LVTTL CMOS logic and can be used for data rates up to 20 Mbps

Loading...

Loading...