MPC5200B Users Guide, Rev. 1

8-28 Freescale Semiconductor

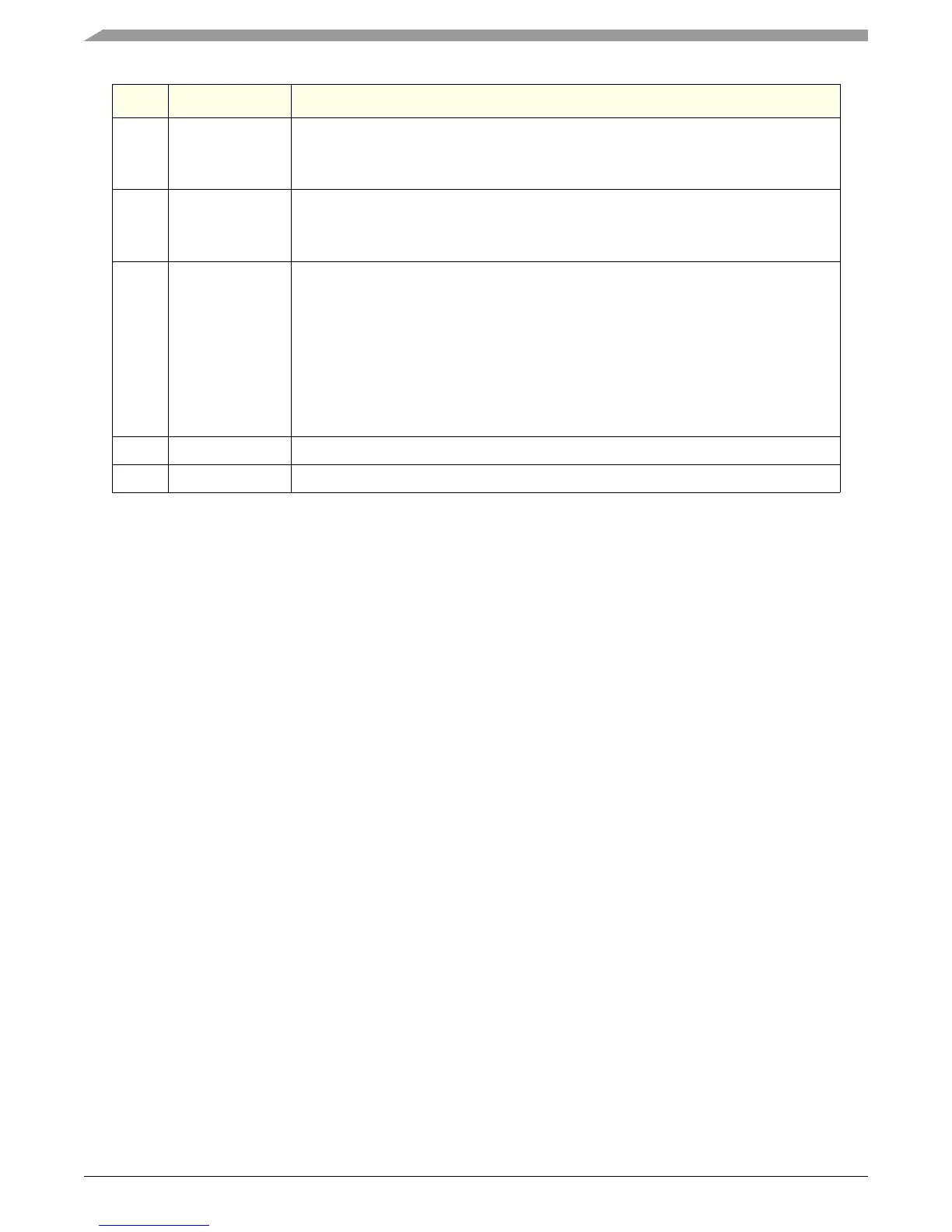

Memory Controller Registers (MBAR+0x0100:0x010C)

Bit Name Description

0:3 brd2rp Burst Read to Read/Precharge delay. Limiting case is Read to Read.

For DDR, suggested value = 0x4 (BurstLength/2)

For SDR, suggested value = 0x8 (BurstLength)

4:7 bwt2rwp Burst Write to Read/Write/Precharge delay. Limiting case is Write to Precharge.

For DDR, suggested value = 0x6 (BurstLength/2 + t

WR

)

For SDR, suggested value = 0x8 (BurstLength + t

WR

- 2)

8:11 brd2wt Burst Read to Read/Write/Precharge delay. Limiting case is Read to Write:

For DDR: CL + burstlength/2 + round trip delay + t

Hz

- 1.5 clk; round up.

If round trip delay = 1 clk and t

Hz

= 0.75 ns:

If CL==2: 2 + 4 + 1 + 0.75ns -1.5 = 5.5clk + 0.75ns, round to 0x6.

If CL==2.5: 2.5 + 4 + 1 + 0.75ns + 1.5 = 6clk + 0.75ns, round to 0x7.

For SDR: CL + burstlength + round trip delay + t

Hz

- 1 clk:

If CL==2: 2 + 8 + 1 + 5.4ns - 1 = 10clk + 5.4ns, round to 0xB.

If CL==3: 3 + 8 + 1 + 5.4ns - 1 = 11clk + 5.4ns, round to 0xC.

12:15 burst_length Write 0x07 (Burst Length - 1)

16:31 — Reserved

Loading...

Loading...