MPC5200B Users Guide, Rev. 1

15-28 Freescale Semiconductor

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

15.2.19 Input Port Register (0x34)—IP

This read-only IP register shows the current state of the input ports.

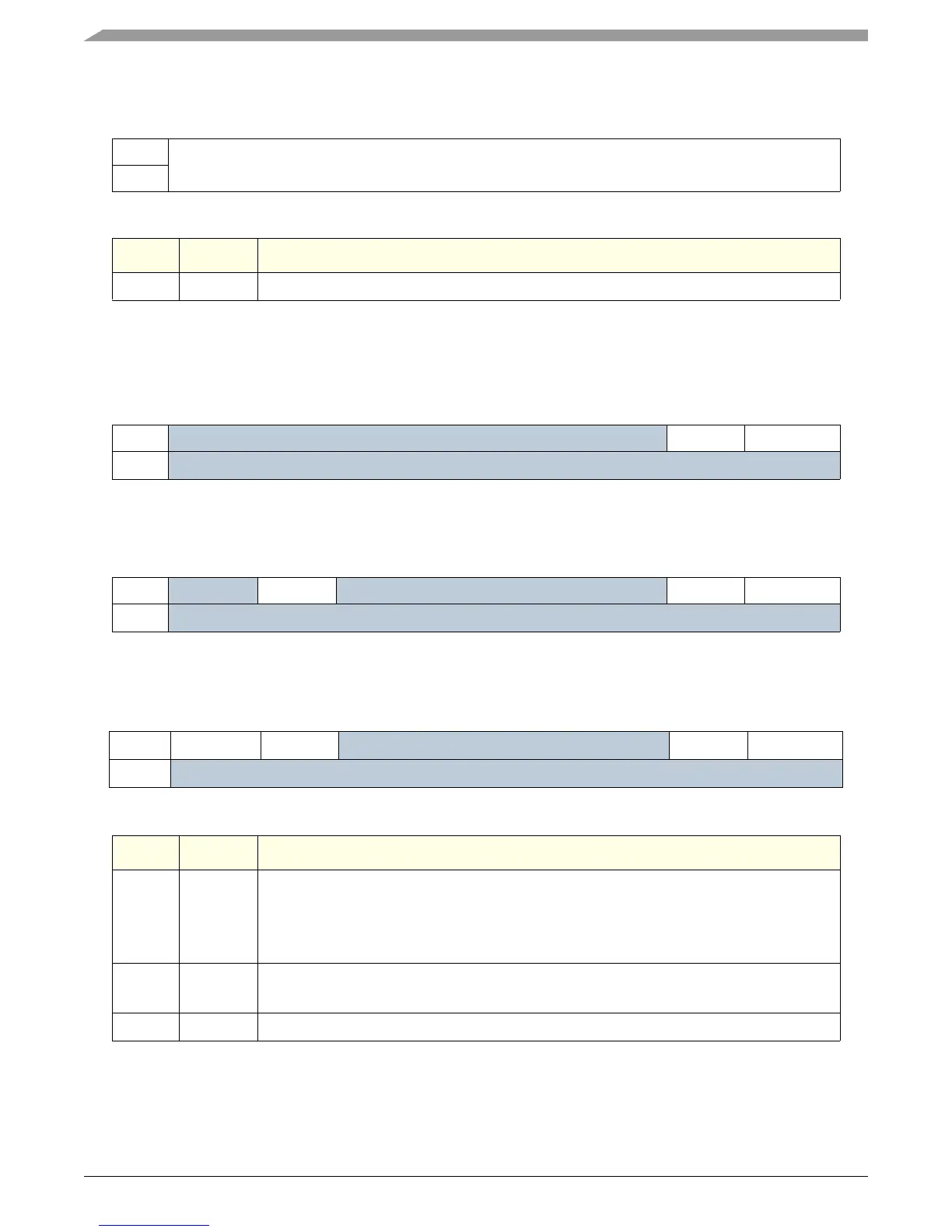

Table 15-38. Interrupt Vector Register (0x30) for all Modes

msb 0 1 2 3 4 5 6 7 lsb

R IVR[0:7]

W

RESET:00000000

Bit Name Description

0:7 IVR Interrupt Vector— Not applicable for MPC5200.

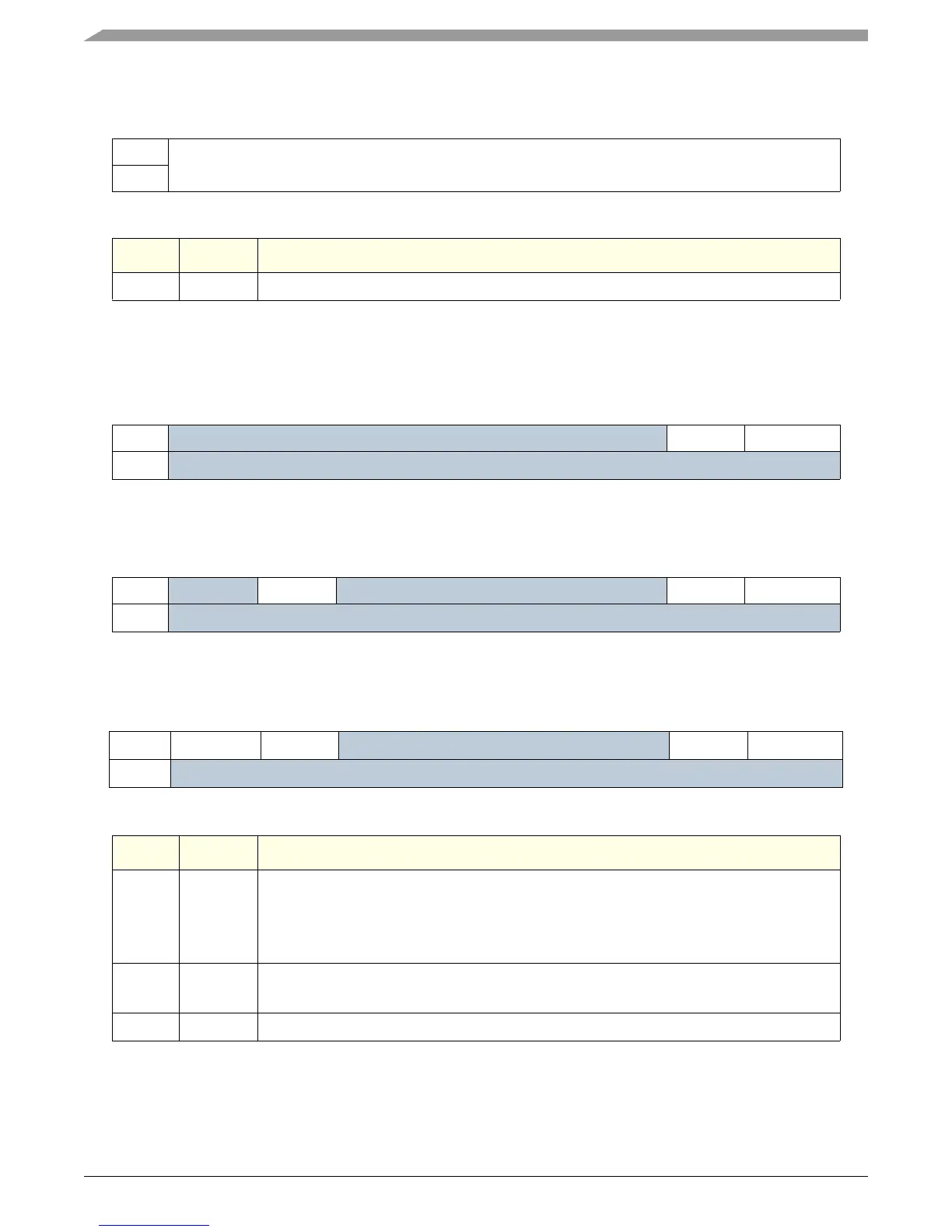

Table 15-39. Input Port Register (0x34) for UART/SIR/MIR/FIR Modes

msb 0 1 2 3 4 5 6 7 lsb

R

Reserved DCD CTS

W

Reserved

RESET:11111100

Table 15-40. Input Port Register (0x34) for Codec Mode

msb 0 1 2 3 4 5 6 7 lsb

R

Reserved TGL Reserved DCD CTS

W

Reserved

RESET:10111100

Table 15-41. Input Port Register (0x34) for AC97 Mode

msb 0 1 2 3 4 5 6 7 lsb

RLPWRTGL Reserved DCD CTS

W Reserved

RESET: 1 1111100

Bit Name Description

0LPWRAC97—Low power mode in AC97 mode

0 = Codec is in low power mode.

1 = Usual operation.

other Modes—Reserved

1TGLAC97 / Codec—Test usage. Toggle by FrameSync.

other Modes—Reserved

2:5 — Reserved

Loading...

Loading...