Prerequisite

l The clock daughter board CKMC/CKMD of the SCU board must be in position.

l The OLT must have the BITS clock input resource.

l The CITD board (its BITS clock daughter board must be in position) must work in the

normal state.

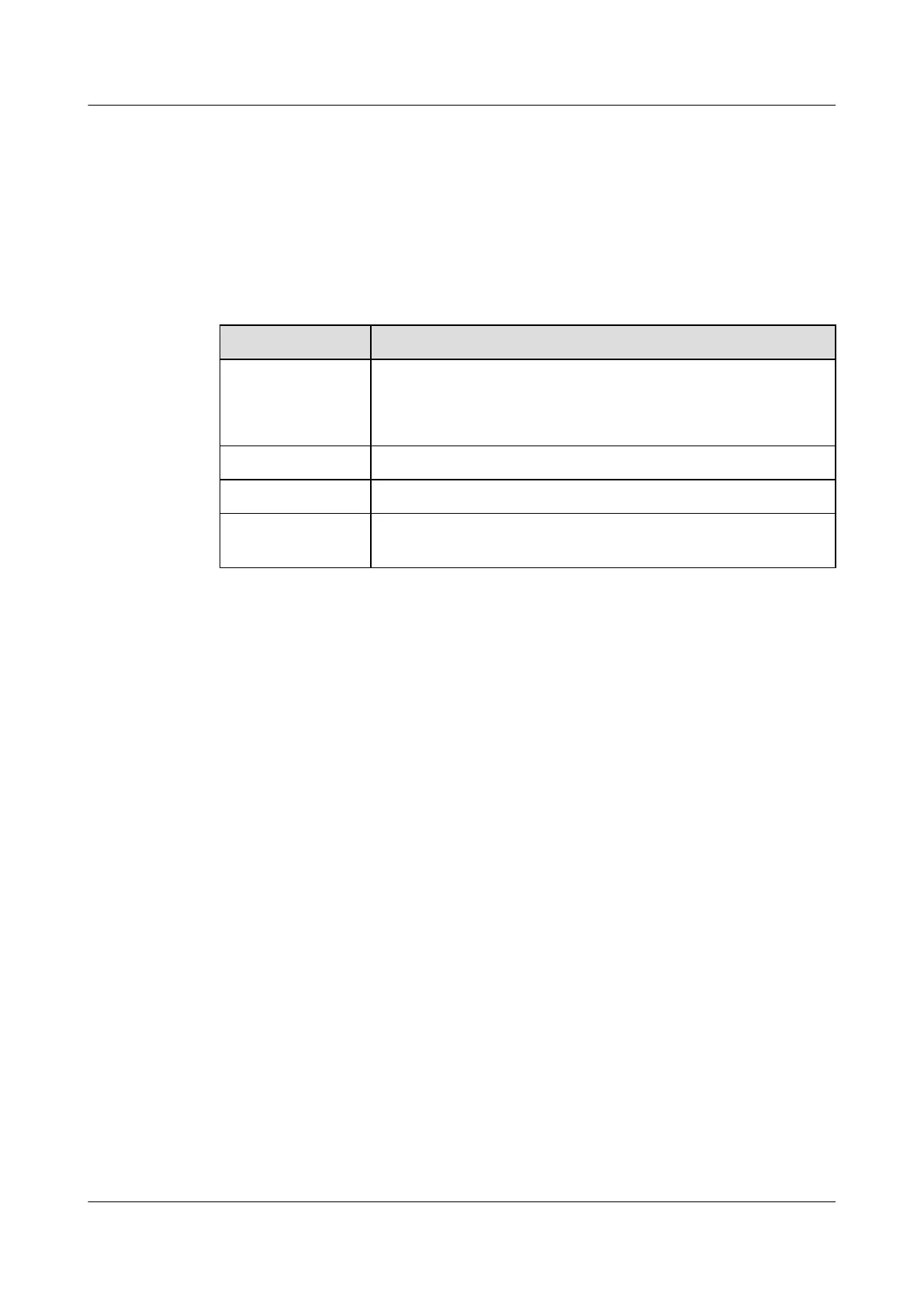

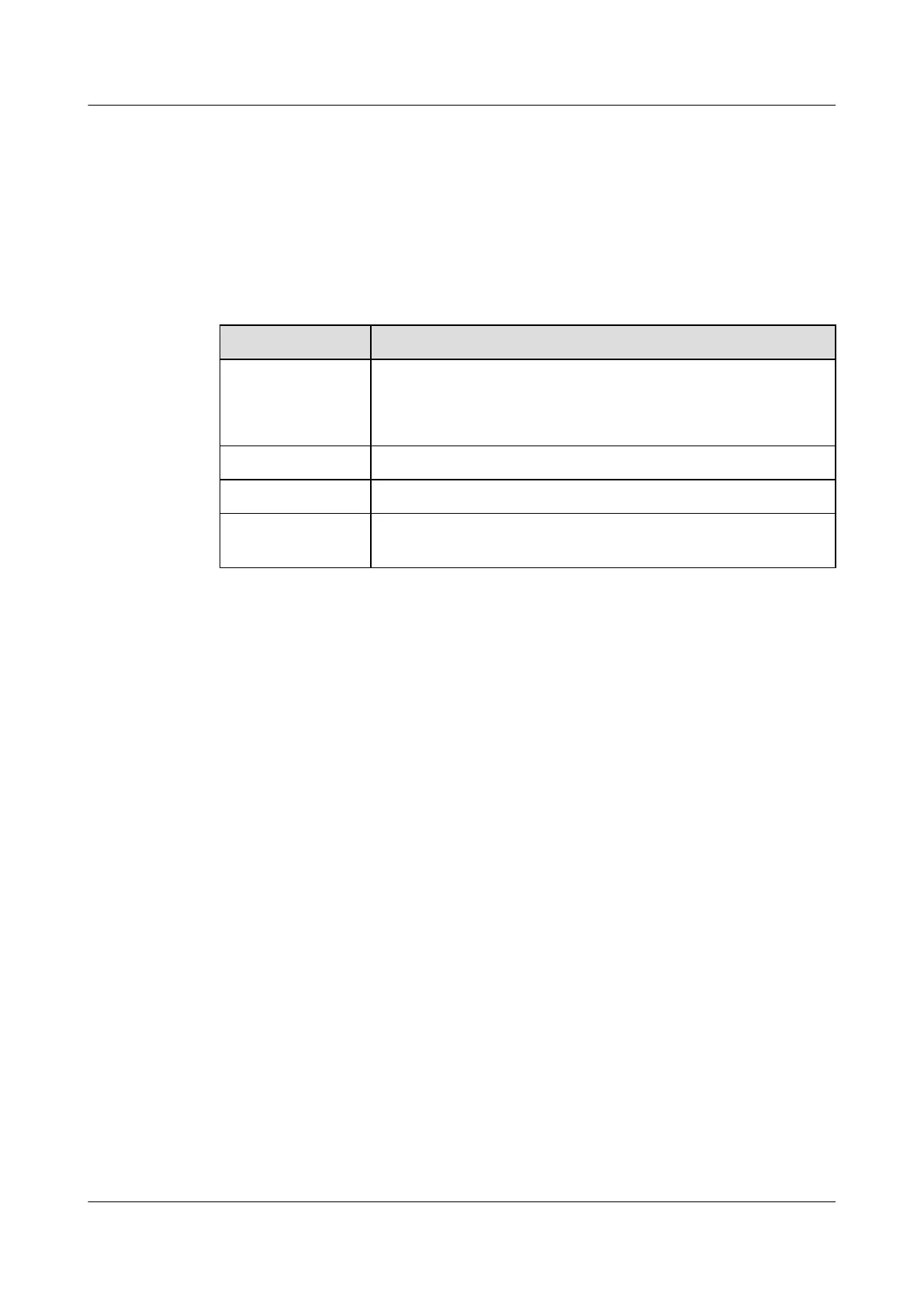

Data Plan

Item Data

CITD board Ports: 0/0/0 and 0/0/1

Clock type: BITS 2 MHz, 120 ohms

Clock priority: p0 > p1

GIU upstream board Port: 0/19/0

E1 port of the ONU 0/1/0

ETH port of the

ONU

0/4/0

Configuration Concept

1. The OLT uses the BITS line clock as the system clock.

2. The system clock is issued to the ONU through the optical path of the PON service board.

3. The ONU uses the line clock of the PON upstream port as the system clock.

4. The E1 Tx clock of the ONU is synchronized to the system clock of the ONU.

Procedure

Step 1 Configure the OLT-side clock.

1. Configure a system clock source.

Run the clock source command to configure BITS_IN ports 0/0/0 and 0/0/1 on the CITD

board as the system clock sources. Set their IDs to 0 and 1 respectively.

huawei(config)#clock source 0 0/0/0 2mhz 120ohm

huawei(config)#clock source 1 0/0/1 2mhz 120ohm

2. Set the priority of the system clock source.

Run the clock priority command to configure the priorities of clock sources 0 and 1 to p0

> P1.

huawei(config)#clock priority system 0/1

3. Query the configuration and status of the system clock source.

Run the display clock source command to query the configuration and status of the clock

source. Ensure that the configuration information about the system clock is matching and

the status is normal.

SmartAX MA5600T/MA5603T/MA5608T Multi-service

Access Module

Commissioning and Configuration Guide

14 FTTM Configuration (Base Station Access)

Issue 01 (2014-04-30) Huawei Proprietary and Confidential

Copyright © Huawei Technologies Co., Ltd.

1382

Loading...

Loading...