Board Design Guidelines for SmartFusion2 SoC and IGLOO2 FPGAs

AC393 Application Note Revision 14.0 24

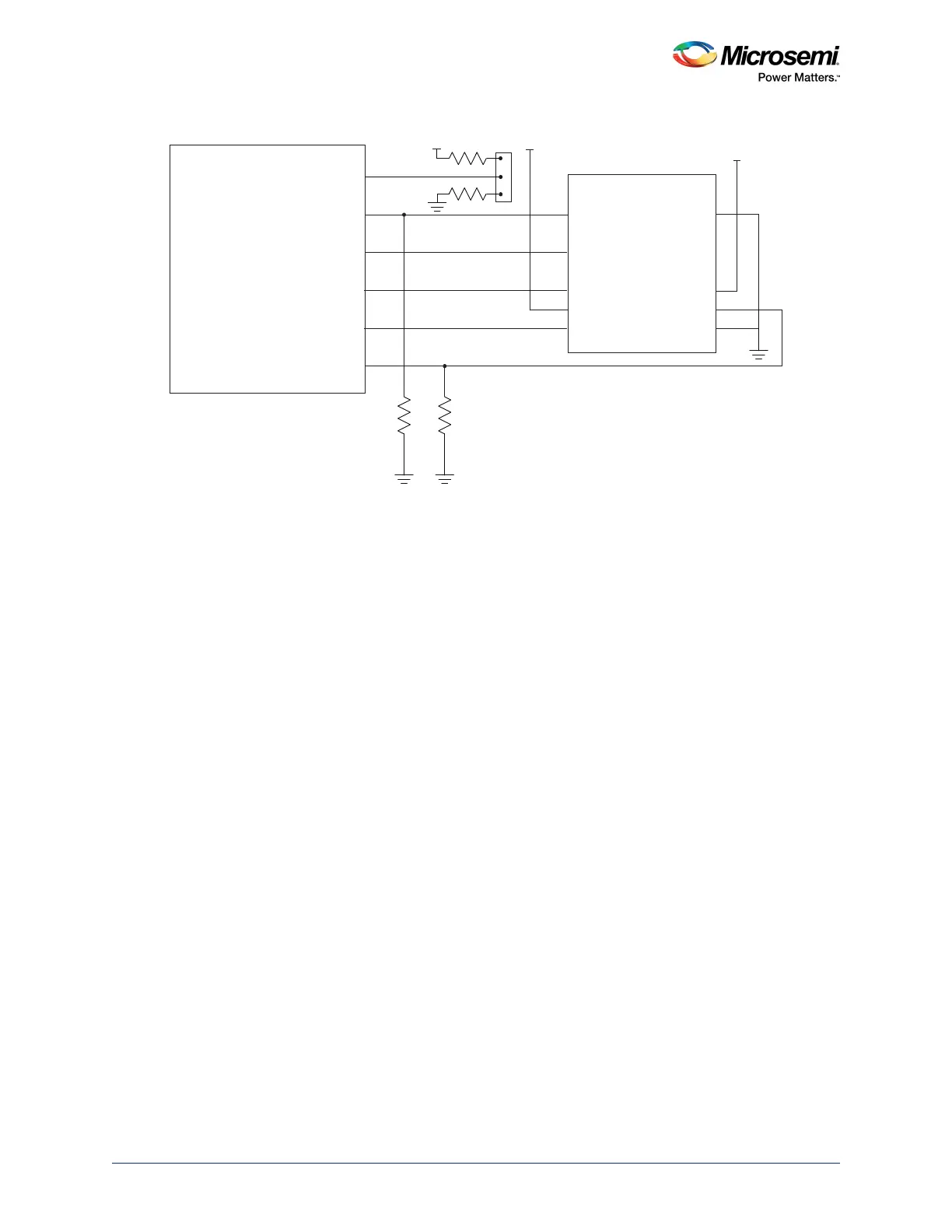

Figure 11 • JTAG Programming

2.7.2 SPI Master Programming

The SmartFusion2/IGLOO2 devices have dedicated pins for programming the device and probing the

fabric I/O.

The embedded system controller contains a dedicated SPI block for programming, which can operate in

master or slave mode. In master mode, the SmartFusion2/IGLOO2 device interfaces with the external

SPI flash from which programming data is downloaded. In slave mode, the SPI block communicates with

a remote device that initiates download of programming data to the device.

Figure 12, page 25 shows the board-level connectivity for SPI master mode programming in

SmartFusion2 and IGLOO2 devices.

VDDI (JTAG)

1 kΩ

1 kΩ

1

2

3

4

5

6

7

8

9

10

SmartFusion2/IGLOO2

JTAGSEL

JTAG_TCK

JTAG_TDO

JTAG_TMS

JTAG_TDI

JTAG_TRSTB

FlashPro4

Header

1 kΩ

1 kΩ

VDDI (JTAG)

VDDI (JTAG)

1

2

3

Loading...

Loading...