Board Design Guidelines for SmartFusion2 SoC and IGLOO2 FPGAs

AC393 Application Note Revision 14.0 33

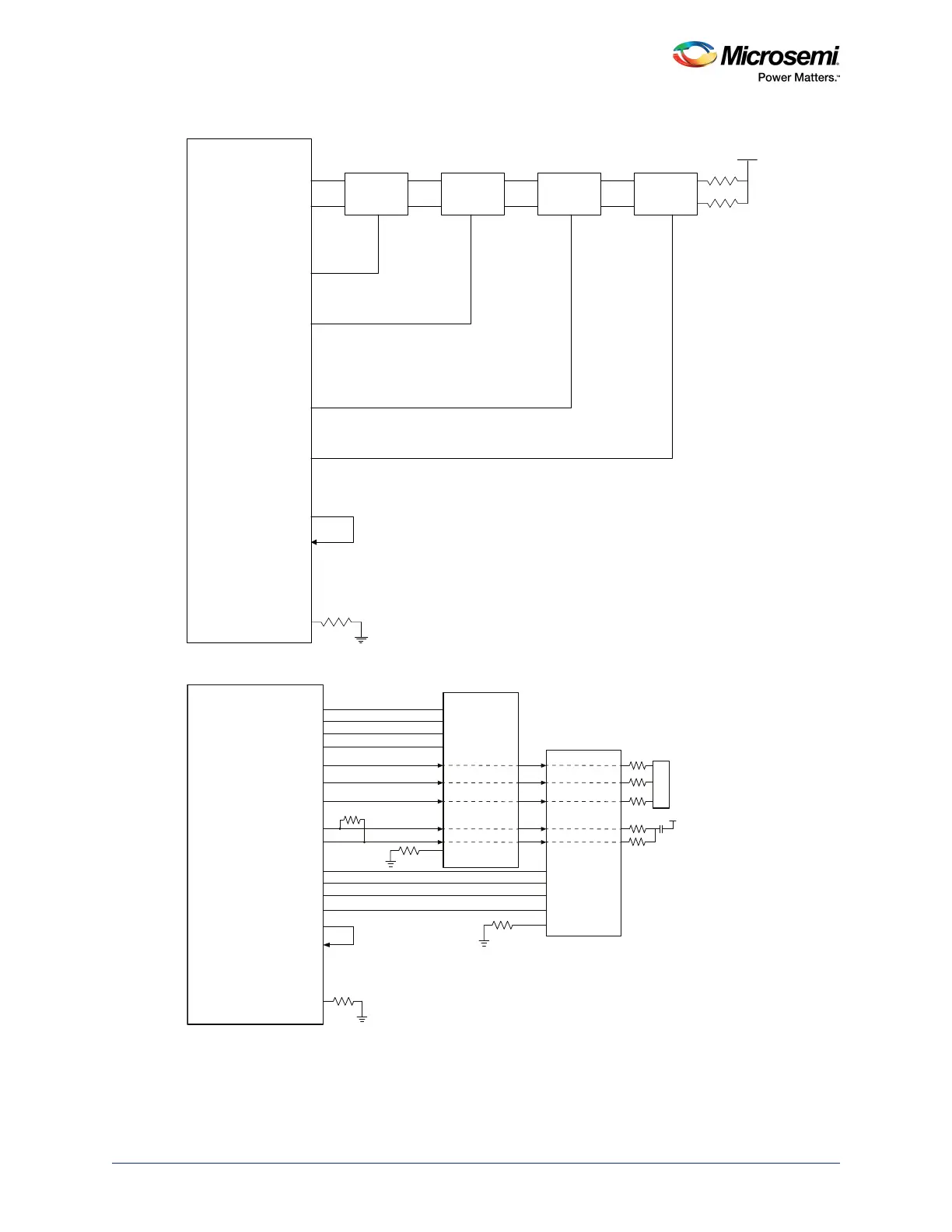

Figure 19 • 8-Bit DDR3 Interface

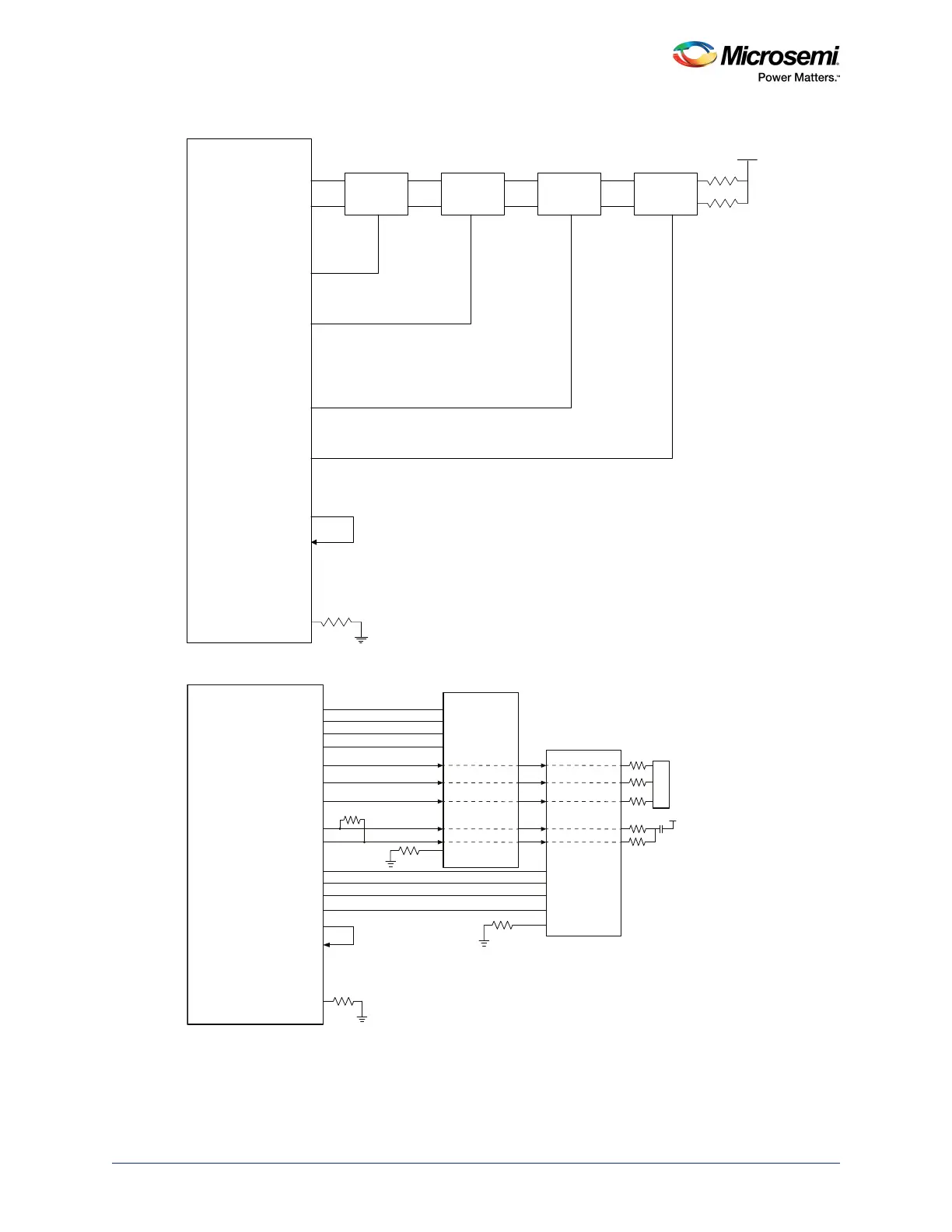

Figure 20 • 16-Bit DDR3 Interface

Note: Short ECC_TMATCH_ OUT and ECC_TMATCH_ IN when using ECC bits.

SmartFusion2/

IGLOO2

DDR3

SDRAM

DDR3

SDRAM

DDR3

SDRAM

DDR3

SDRAM

VTT

Clock

Address and

Command

DQ Group 0

DQ Group 1

DQ Group 2

DQ Group 3

DDR_TMATCH_OUT

DDR_TMATCH_IN

DDR_TMATCH_ECC_OUT

DDR_TMATCH_ECC_IN

DDR_IMP_CALIB_ECC

240 Ω_1%

SmartFusion2/IGLOO2

xDDR_CLK

xDDR_CLK_N

Control Lines

VDD

49.9 Ω

VTT

240 Ω

240 Ω_1%

240 Ω

ZQ

ZQ

100 Ω

xDDR_TMATCH_OUT

xDDR_TMATCH_IN

xDDR_TMATCH_ECC_OUT

xDDR_TMATCH_ECC_IN

xDDR_IMP_CALIB_ECC

xDDR_DQS [1:0]

xDDR_DQS [1:0]_N

xDDR_DM_RDQS [1:0]

xDDR_DQ [15:0]

xDDR_BA [2:0]

xDDR_ADDR [13:0]

xDDR_DQS [3:2]

xDDR_DQS [3:2]_N

xDDR_DM_RDQS [3:2]

xDDR_DQ [31:16]

16 DDR3 SDRAM

x

16 DDR3 SDRAM

x

CKE, CS, WE, RAS, CAS, ODT

49.9 Ω

49.9 Ω

Loading...

Loading...