Board Design Guidelines for SmartFusion2 SoC and IGLOO2 FPGAs

AC393 Application Note Revision 14.0 36

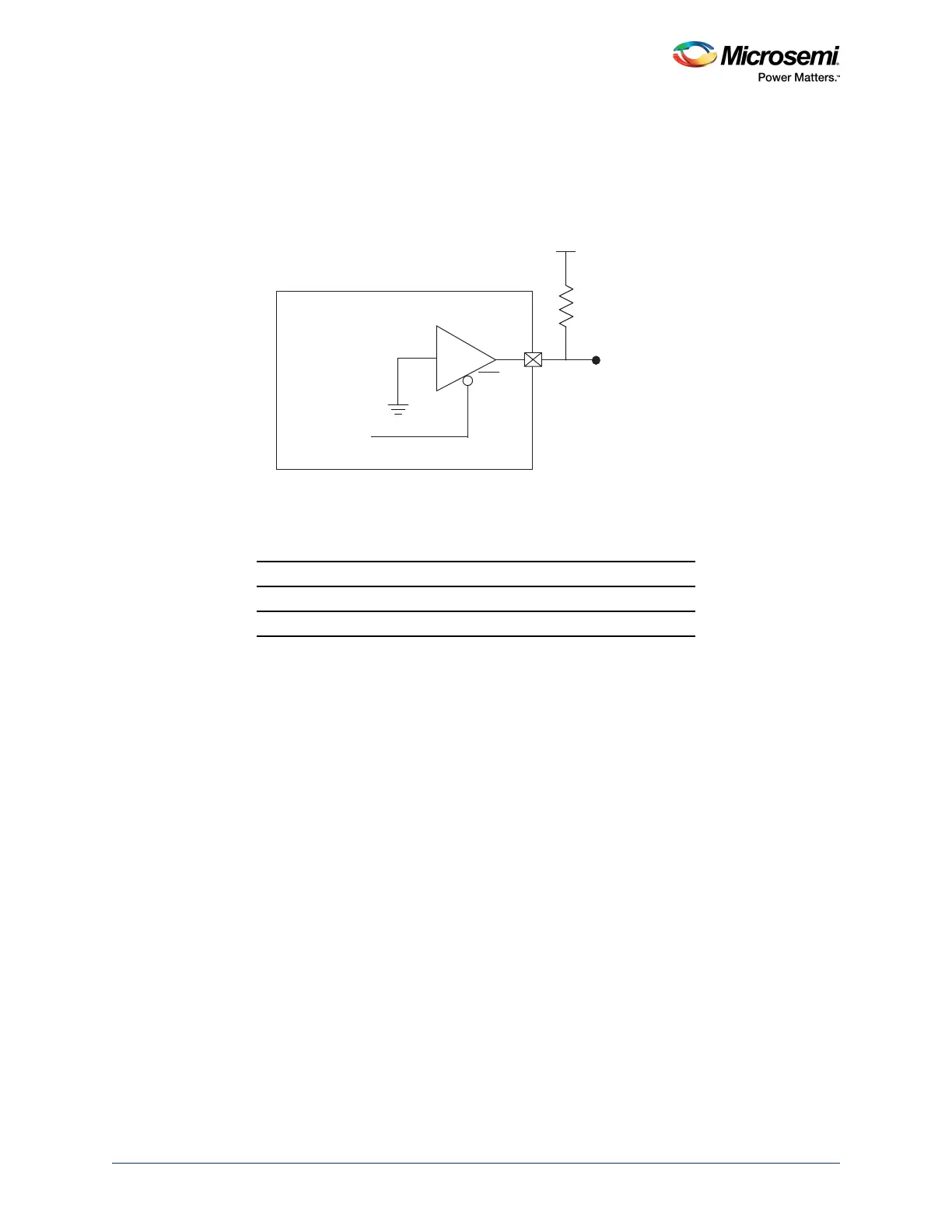

2.12 Configuring Pins in Open Drain

To configure fabric pins in open-drain mode, the input port of the tristate buffer must be tied low, and the

enable port of the buffer must be driven from the user logic via the fabric port, as shown in the following

figure.

Figure 22 • Configuring Pins in Open Drain

The following table lists the truth table for configuring pins in open-drain mode.

2.13 Brownout Detection (BOD)

SmartFusion2/IGLOO2 functionality is guaranteed only if VDD is above the recommended level specified

in the datasheet. Brownout occurs when VDD drops below the minimum recommended operating

voltage. As a result, it is not possible to ensure proper or predictable device operation. The design might

continue to malfunction even after the supply is brought back to the recommended values, as parts of the

device might have lost functionality during brownout. The VDD supply must be protected by a brownout

detection circuit.

To recover from VDD brownout, the device must either be power-cycled, or an external brownout

detection circuit must be used to reset the device for correct operation. The recommended guideline for

the threshold voltage of brownout detection is mentioned in “Table 14” of DS0128: IGLOO2 and

SmartFusion2 Datasheet. The brownout detection circuit must be designed such that when the VDD falls

below the recommended voltage mentioned in the datasheet, the device is held in power-down mode via

the DEVRST_N pin.

Note: Brownout detection must be implemented through a standalone circuit or included as part of power

management circuitry.

Table 20 • Truth Table

Buffer Enable Port Buffer In Port Buffer Out Port

0 (low) 0 (low) 0 (low)

1 (high) 0 (low) VDDI

X

10 k

I/O Pin

SmartFusion2/IGLOO2

IN

OUT

Fabric Port

EN

VDDIx

Loading...

Loading...