Layout Guidelines for SmartFusion2- and IGLOO2-Based Board Design

AC393 Application Note Revision 14.0 48

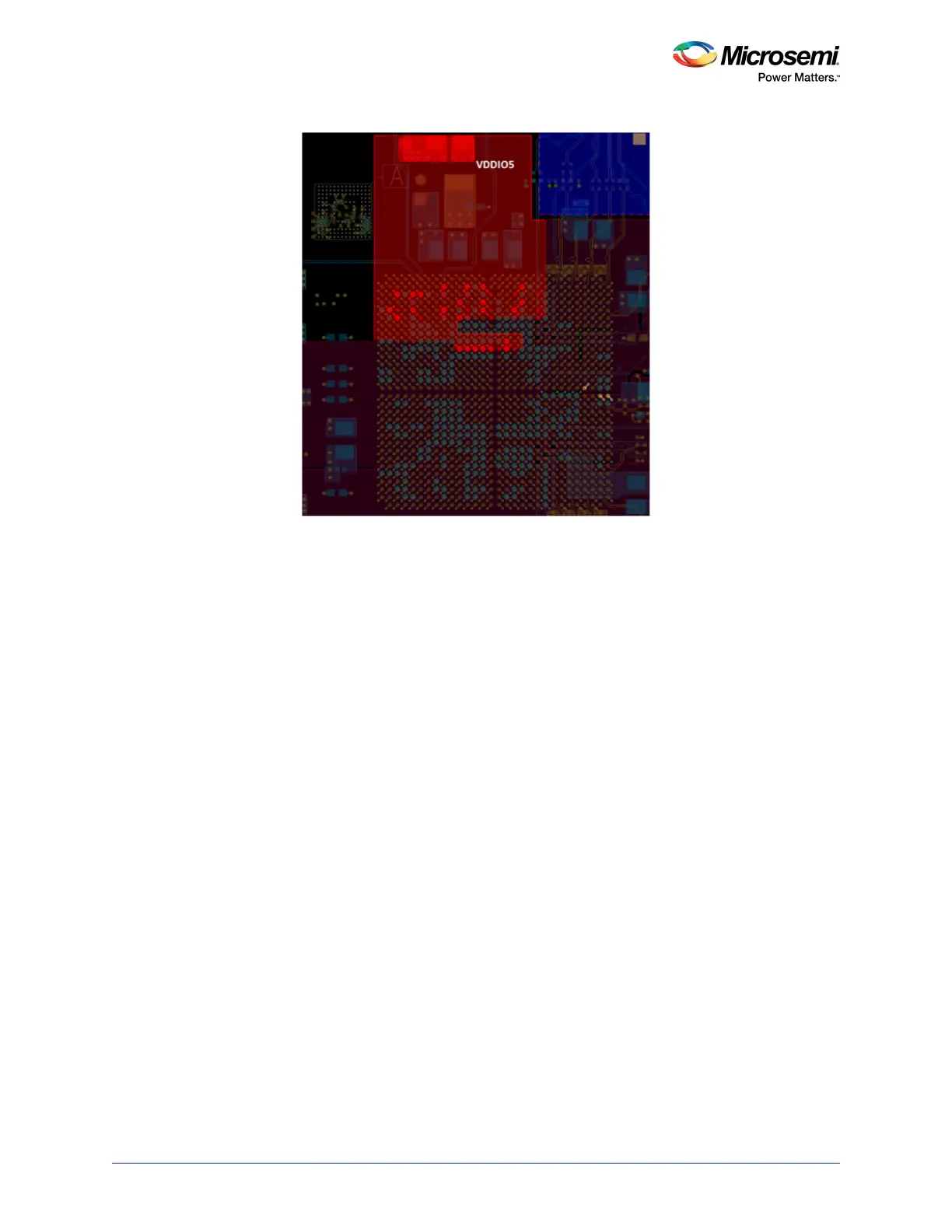

Figure 37 • Layout of VDDIO5 Plane

3.4.3 Simulations

The target impedance of the DDR VDDIO is calculated as 240 mΩ, based on the values (see Power

Supply, page 38):

•V

SUPPLY

= 1.5V,

•I

trans

= 250 mA

• Ripple = 5%

The impedance profile of the DDR VDDIO plane over frequency range is shown in the following figures.

The impedance improves with the decoupling capacitors provided. The target impedance of 0.3 Ω has

been achieved till 500 MHz.

Loading...

Loading...