11. Timer 0/1/2 A96G166/A96A166/A96S166 User’s manual

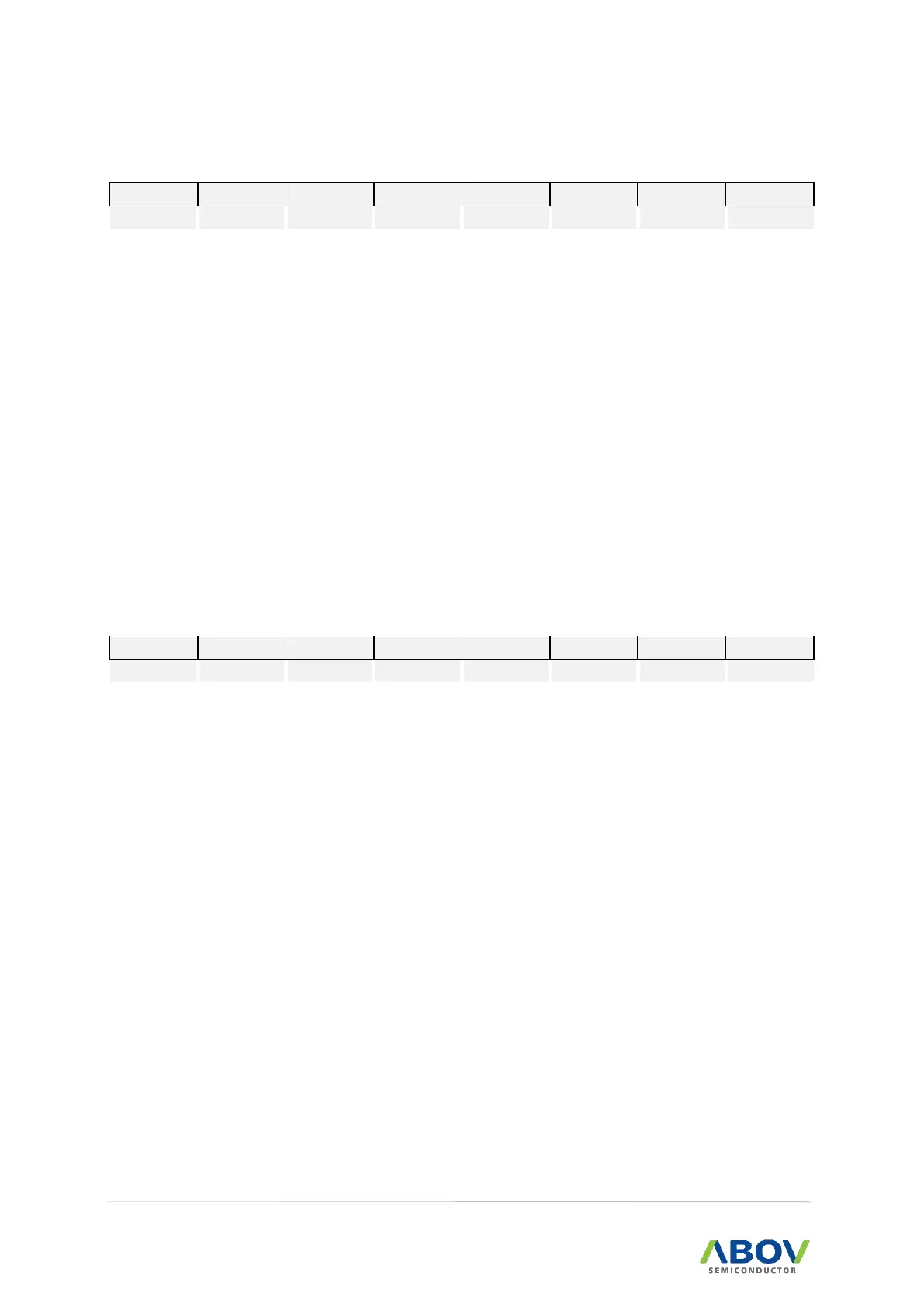

T1CRH (Timer 1 Control High Register): BBH

Timer 1 enable (Counter clear and start)

Control Complementary PWM

Complementary PWM disable

Control Timer 1 Operation Mode

Timer/counter mode (T1O: toggle at A match)

Capture mode (The A match interrupt can

occur)

PPG one-shot mode (PWM1O)

Control Timer 1 port output

Clear the Timer 1 counter (When write, automatically

cleared “0” after being cleared counter)

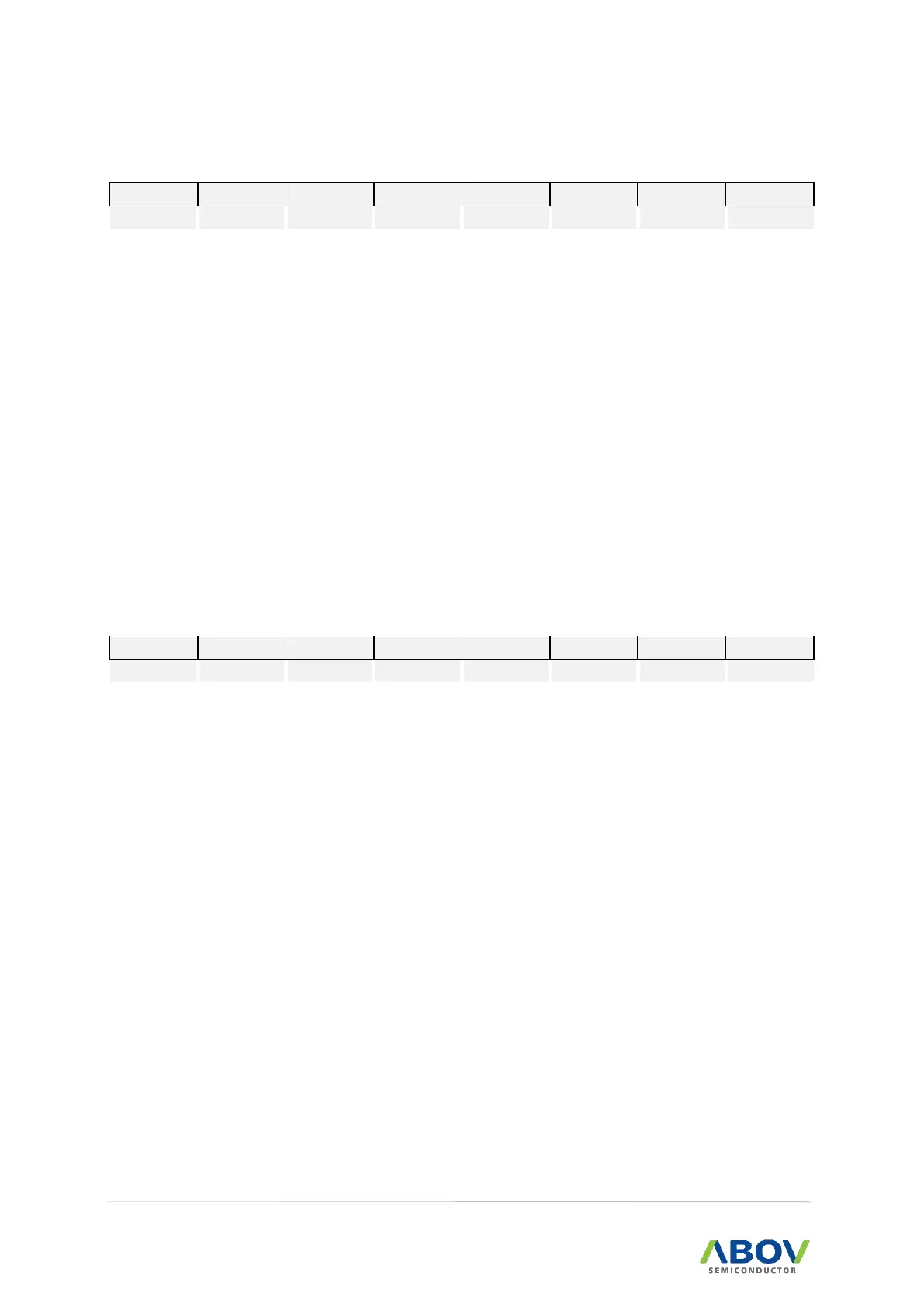

T1CRL (Timer 1 Control Low Register): BAH

Select Timer 1 clock source. fx is main system clock frequency

When T1 Interrupt occurs, this bit becomes ‘1’. For clearing bit, write ‘0’

to this bit or auto clear by INT_ACK signal. Writing “1” has no effect.

T1 Interrupt no generation

PWM1OB Polarity Selection

Start High (PWM1OB is low level at disable)

Start Low (PWM1OB is high level at disable)

T1O/PWM1O Polarity Selection

Start High (T1O/PWM1O is low level at disable)

Start Low (T1O/PWM1O is high level at disable)

Timer 1 External Clock Edge Selection

External clock falling edge

External clock rising edge

Timer 1 Counter Read Control

Load the counter value to the B data register (When write,

automatically cleared “0” after being loaded)

Loading...

Loading...