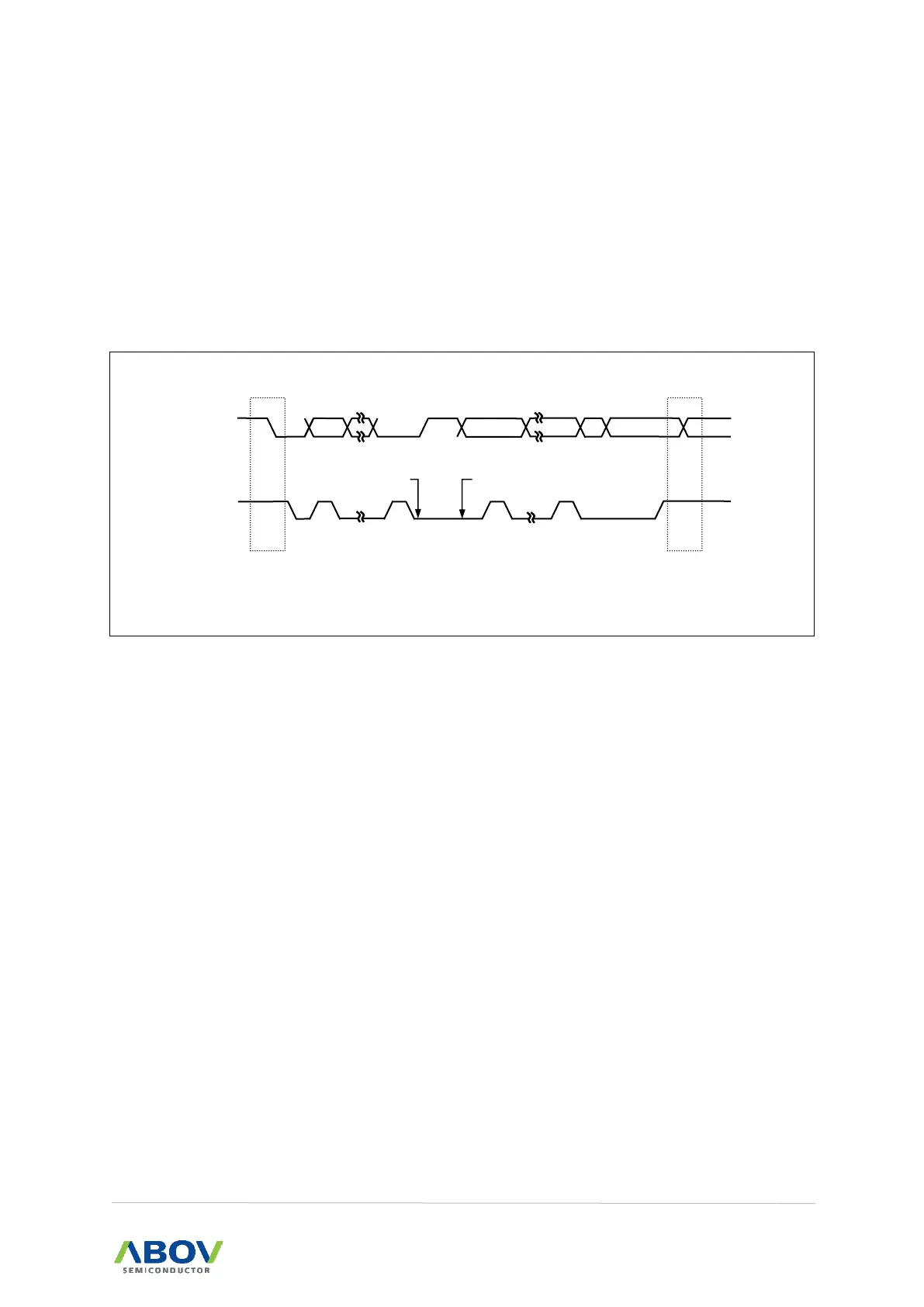

14.4 Data transfer

Every byte on the SDA line must be 8-bits long. The number of bytes that can be transmitted per

transfer is unlimited. Each byte has to be followed by an acknowledge bit. Data is transferred with the

most significant bit (MSB) first. If a slave can’t receive or transmit another complete byte of data until it

has performed some other function, it can hold the clock line SCL LOW to force the master into a wait

state. Data transfer then continues when the slave is ready for another byte of data and releases

clock line SCL.

Figure 65. Data Transfer on the I2C-Bus

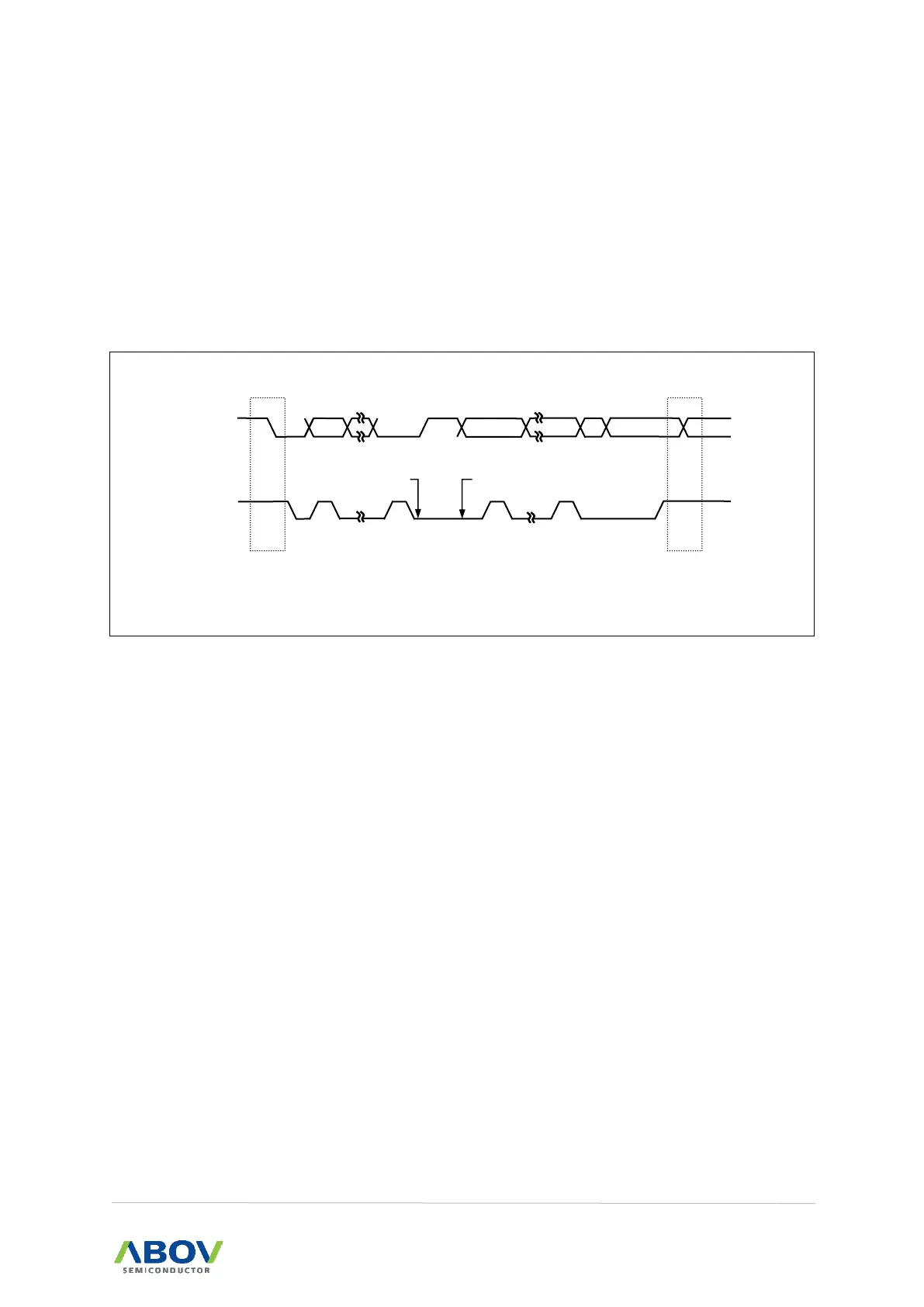

14.5 Acknowledge

The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA

line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the

acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse.

When a slave is addressed by a master (Address Packet), and if it is unable to receive or transmit

because it’s performing some real time function, the data line must be left HIGH by the slave. And

also, when a slave addressed by a master is unable to receive more data bits, the slave receiver must

release the SDA line (Data Packet).

The master can then generate either a STOP condition to abort the transfer, or a repeated START

condition to start a new transfer.

If a master receiver is involved in a transfer, it must signal the end of data to the slave transmitter by

not generating an acknowledge on the last byte that was clocked out of the slave. The slave

transmitter must release the data line to allow the master to generate a STOP or repeated START

condition.

Loading...

Loading...