A96G166/A96A166/A96S166 User’s manual 9. Watchdog timer

9.4 Register description

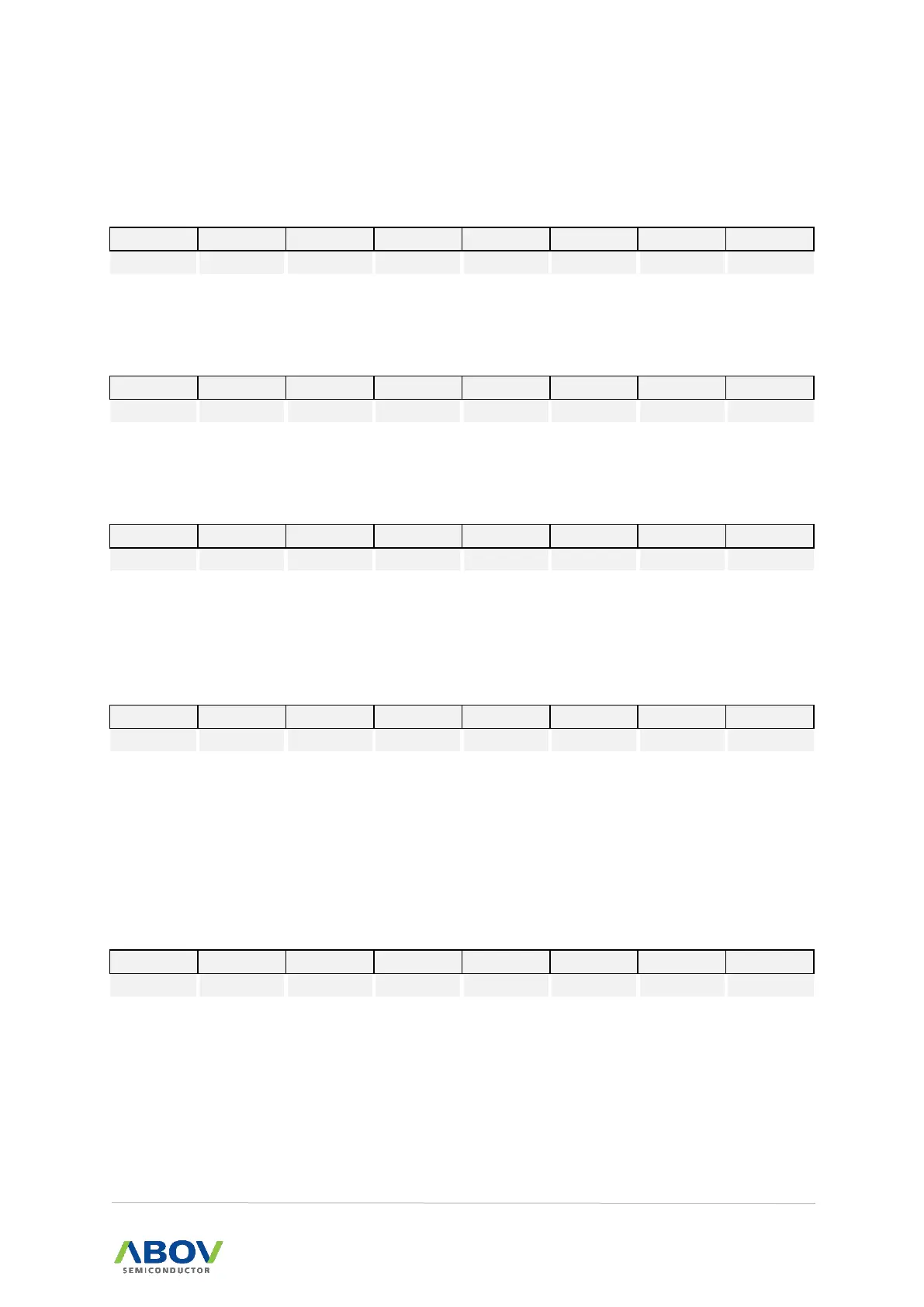

WDTCNTH (Watch Dog Timer Counter High Register): 1012H

WDTCNTL (Watch Dog Timer Counter Low Register): 1013H

WDTC (Watch Dog Timer Clear Register): 1010H

WDT counter clear and start again

WDTSR (Watch Dog Timer Status Register): 1011H

When WDT Interrupt occurs, this bit becomes ‘1’. For clearing bit, write

‘0’ to this bit or auto clear by INT_ACK signal.

WDT Interrupt no generation.

WDT Interrupt generation.

WDTIDR (Watch Dog Timer Identification Register): 8EH

WDT Identification for a WDTCR

Identification value for a WDTCR write.

NOTE: These bits are automatically cleared to logic ‘00H’

immediately after WDTCR write.

Loading...

Loading...