MB95630H Series

MN702-00009-2v0-E FUJITSU SEMICONDUCTOR LIMITED 573

CHAPTER 26 DUAL OPERATION FLASH MEMORY

26.8 Registers

[bit4] CERTO: CERTO interrupt request flag bit

This bit indicates that Flash memory chip erase has failed.

When Flash memory chip erase fails, the CERTO bit is set to "1" upon completion of the Flash memory

automatic algorithm.

An interrupt request is generated when the CERTO bit is set to "1", provided that generating an interrupt

request upon failure of Flash memory chip erase has been enabled (FSR4:CTIEN = 1).

When the CERTO bit is set to "1" after Flash memory chip erase is completed, further Flash memory

programming/erasing is disabled. Writing a reset command can make the Flash memory return to the normal

command state.

Writing "0" to this bit clears it.

Writing "1" to this bit has no effect on operation.

When read by the read-modify-write (RMW) type of instruction, this bit always returns "1".

[bit3:0] Undefined bits

Their read values are always "0". Writing values to these bits has no effect on operation.

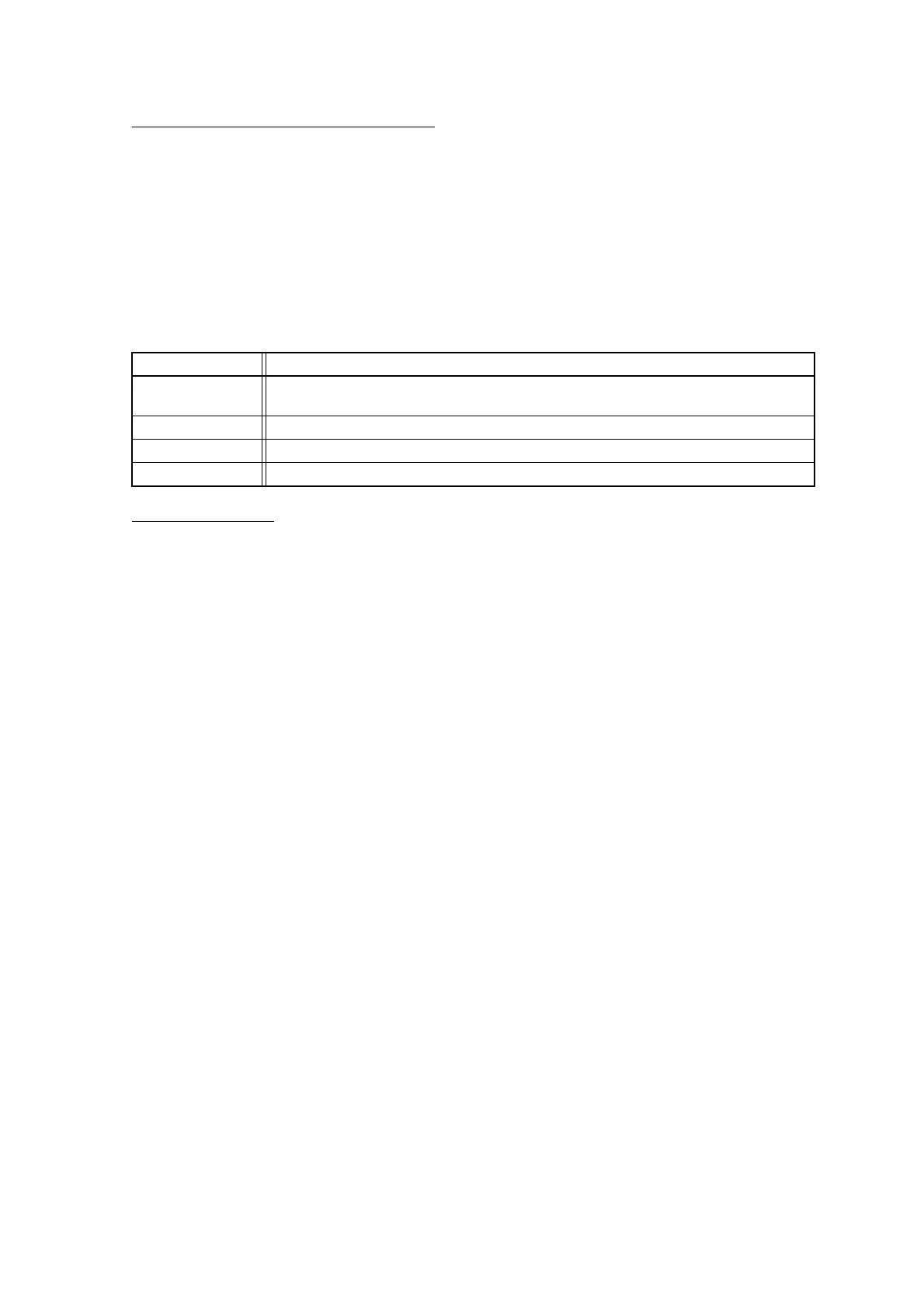

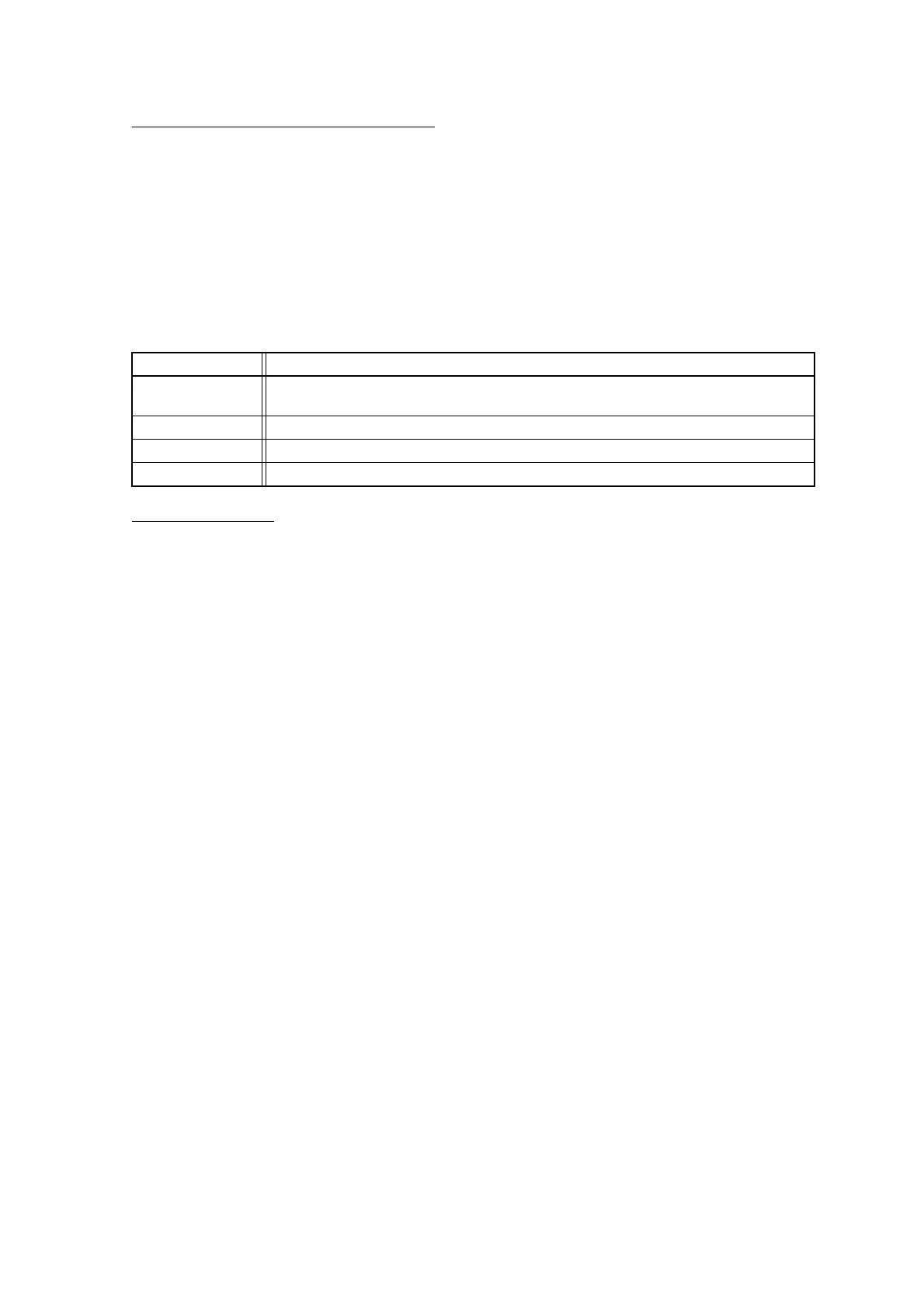

bit4 Details

Reading "0"

Indicates that the device is in the command input wait state or Flash memory chip erase is in

progress.

Reading "1" Indicates that Flash memory chip erase has failed.

Writing "0" Clears this bit.

Writing "1" Has no effect on operation.

Loading...

Loading...