Intel

®

Server Chassis P4304XXMFEN2/P4304XXMUXX Product Family System Integration and Service Guide

158

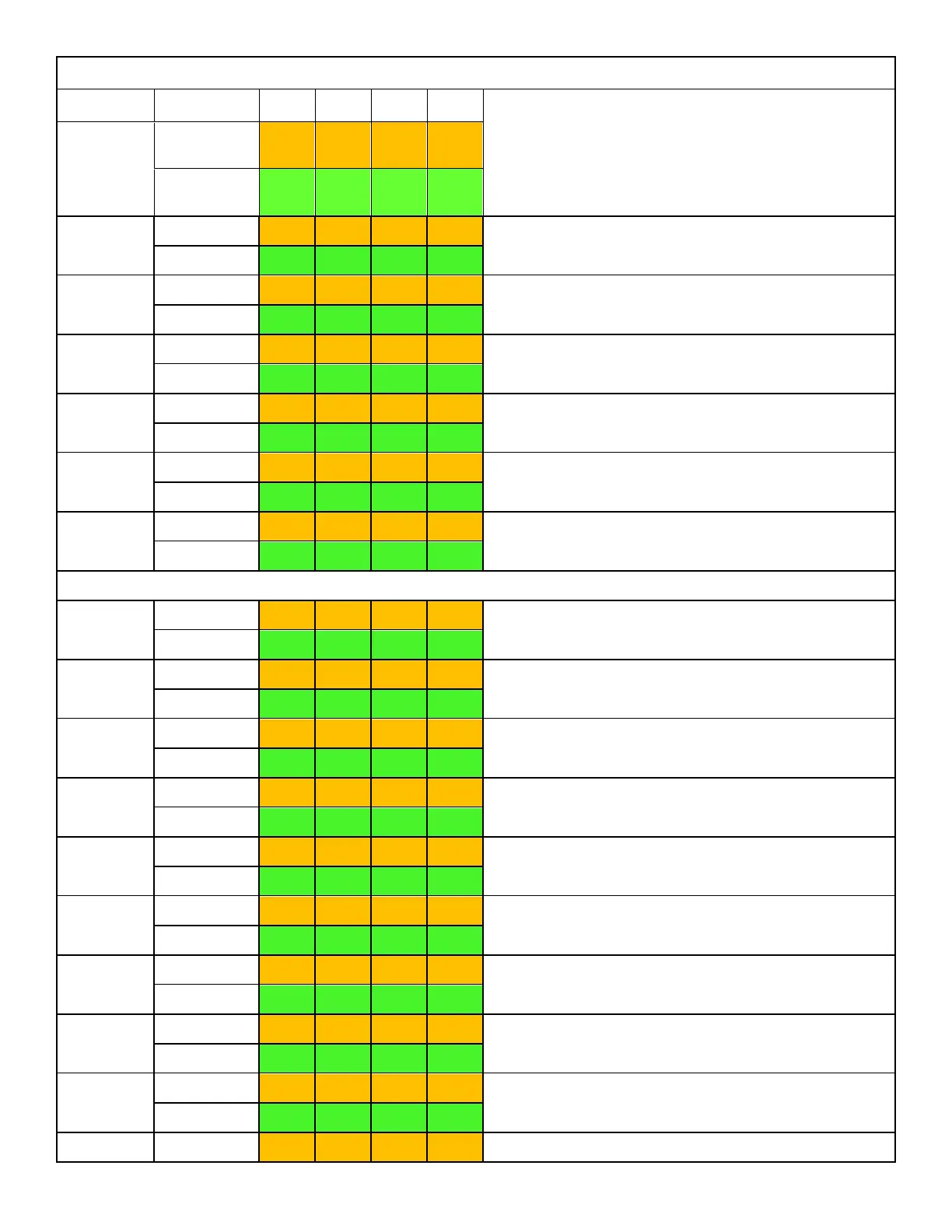

LED 3 LED 2 LED 1 LED 0

Description

Checkpoint

Upper Nibble

(MSB)

4h 2h

(LSB)

Lower Nibble

(MSB)

4h 2h

(LSB)

01h

First POST code after CPU reset

02h

Microcode load begin

03h

CRAM initialization begin

04h

EI Cache When Disabled

05h

SEC Core at Power on Begin

06h

Early CPU Initialization during Sec Phase

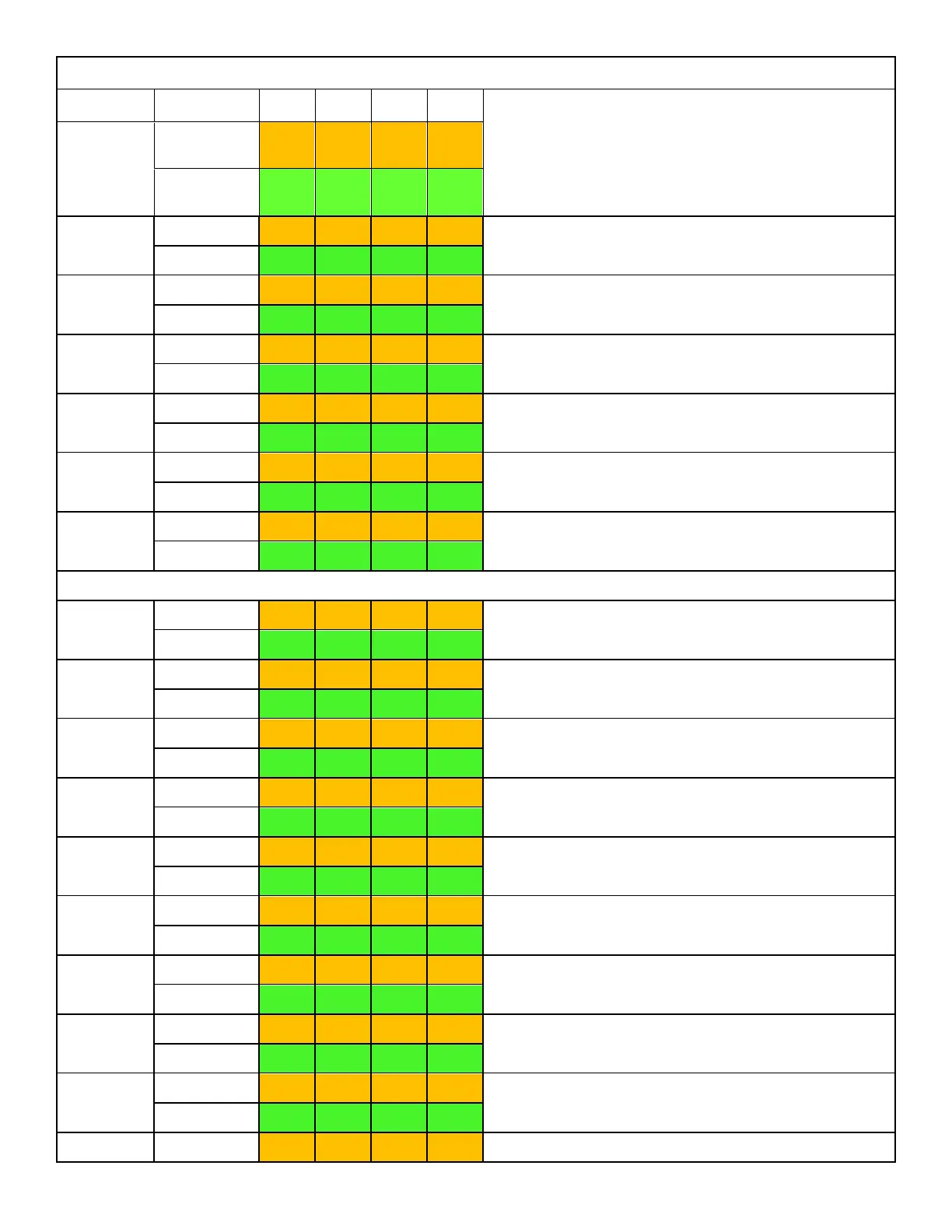

UPI RC (Fully leverage without platform change)

A1h

Collect Info such as SBSP, Boot Mode, Reset Type Etc.

A3h

Set Up Minimum Path Between SBSP & Other Sockets

A7h

Topology Discovery and Route Calculation

A8h

Program Final Route

A9h

Program Final IO SAD Setting

AAh

Protocol Layer and Other Uncore Settings

ABh

Transition Links to Full Speed Operation

Ach

PHY Layer Setting

ADh

Link Layer Settings

Loading...

Loading...