Chapter 04 Appendix

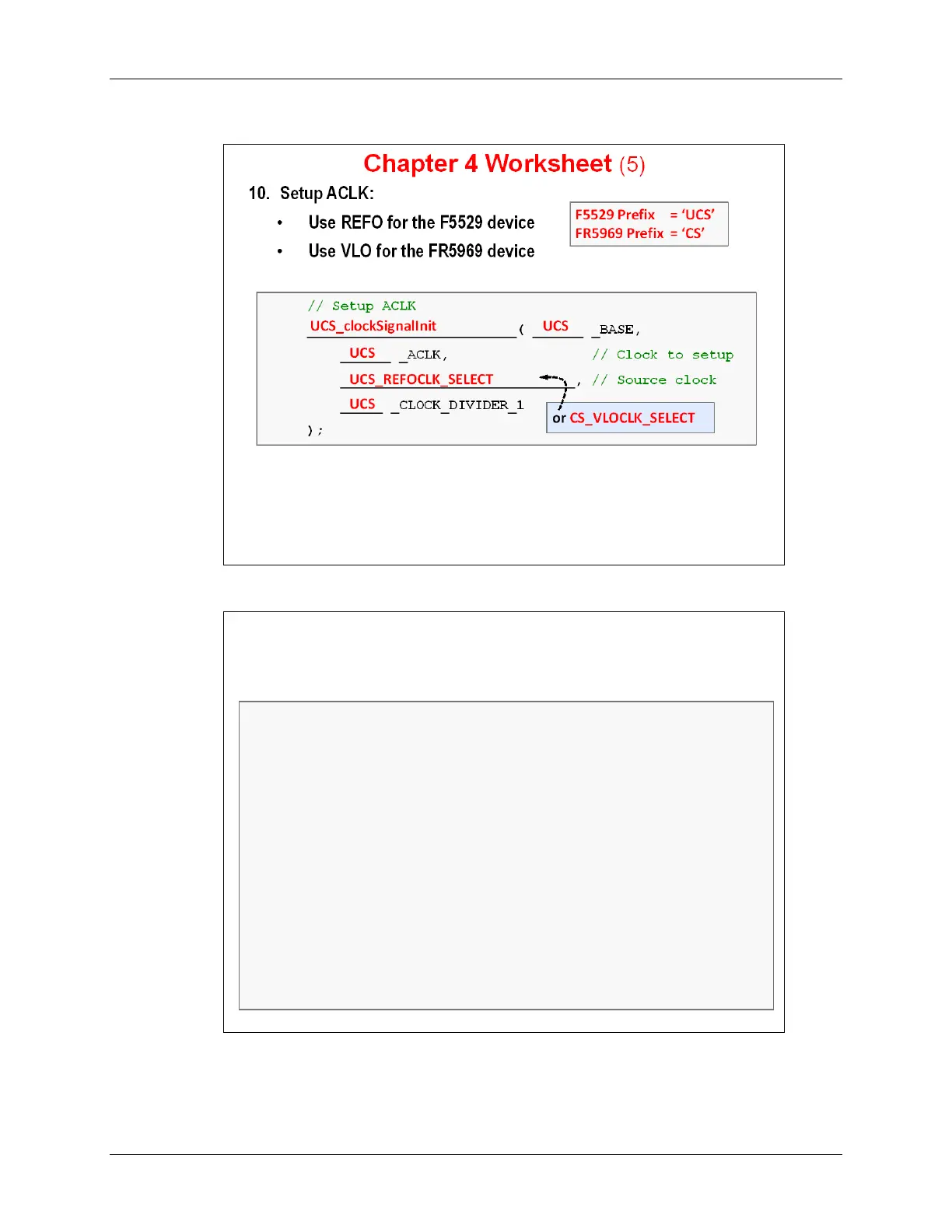

Chapter 4 Worksheet (6)

11. (F5529 User’s only) Write the code to setup MCLK. It should be

running at 8MHz using the DCO as its oscillator source.

#define MCLK_DESIRED_FREQUENCY_IN_KHZ _________________________

#define MCLK_FLLREF_RATIO __________________________ /(UCS_REFOCLK_FREQUENCY/1024 )

// Set the FLL's clock reference clock to REFO

_________________________( UCS_BASE,

UCS_FLLREF, // Clock you're configuring

_____________________, // Clock Source

UCS_CLOCK_DIVIDER_1 );

//

Config the FLL's freq, let it settle, and set MCLK & SMCLK to use DCO+FLL as clk source

_________________________( UCS_BASE,

MCLK_DESIRED_FREQUENCY_IN_KHZ,

_____________________________);

8000

MCLK_DESIRED_FREQUENCY_IN_KHZ

UCS_clockSignalInit

UCS_REFOCLK_SELECT

UCS_initFLLSettle

MCLK_FLLREF_RATIO

4 - 62 MSP430 Workshop - MSP430 Clocks & Initialization

Loading...

Loading...