Interrupts and TI-RTOS Scheduling

Hwi – Swi – Idle Scheduling

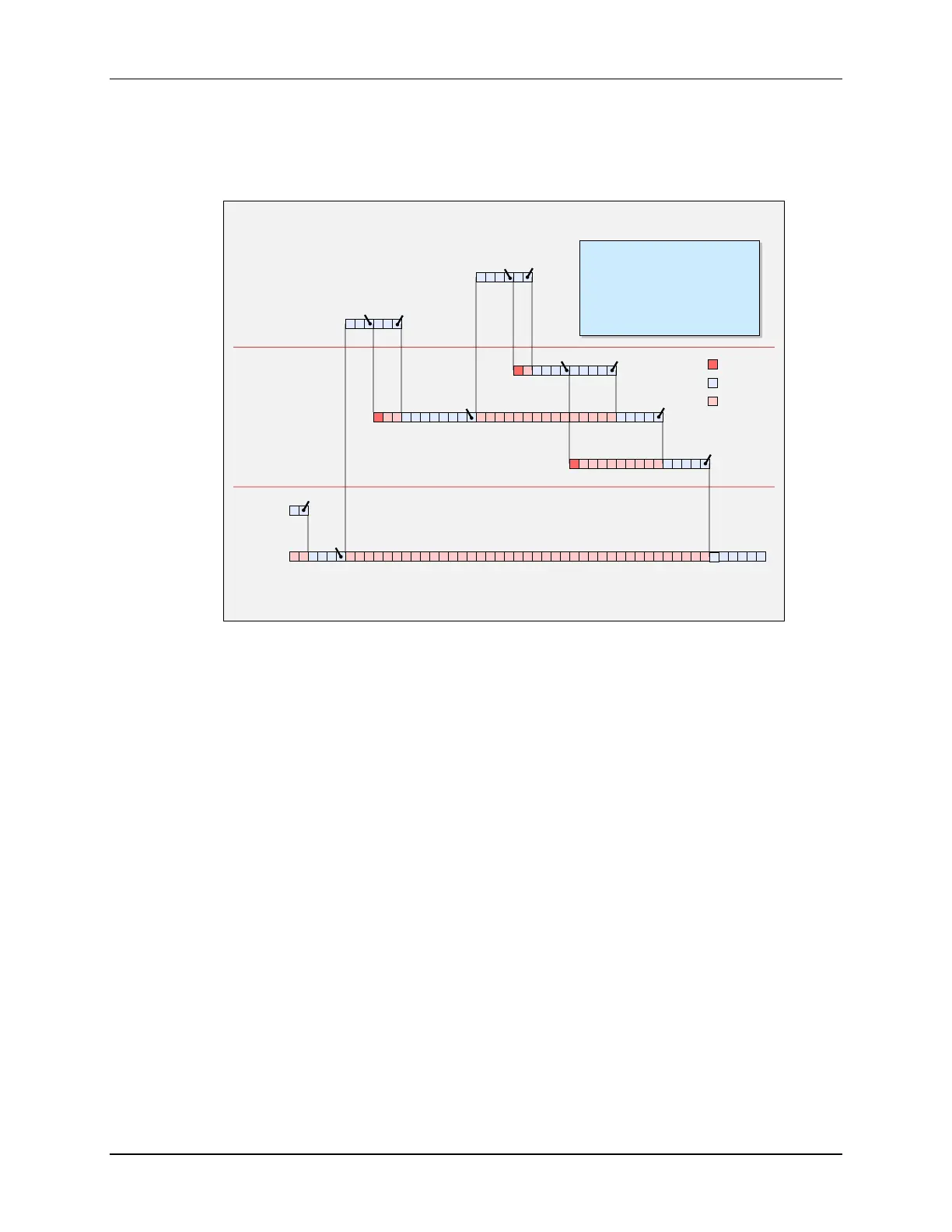

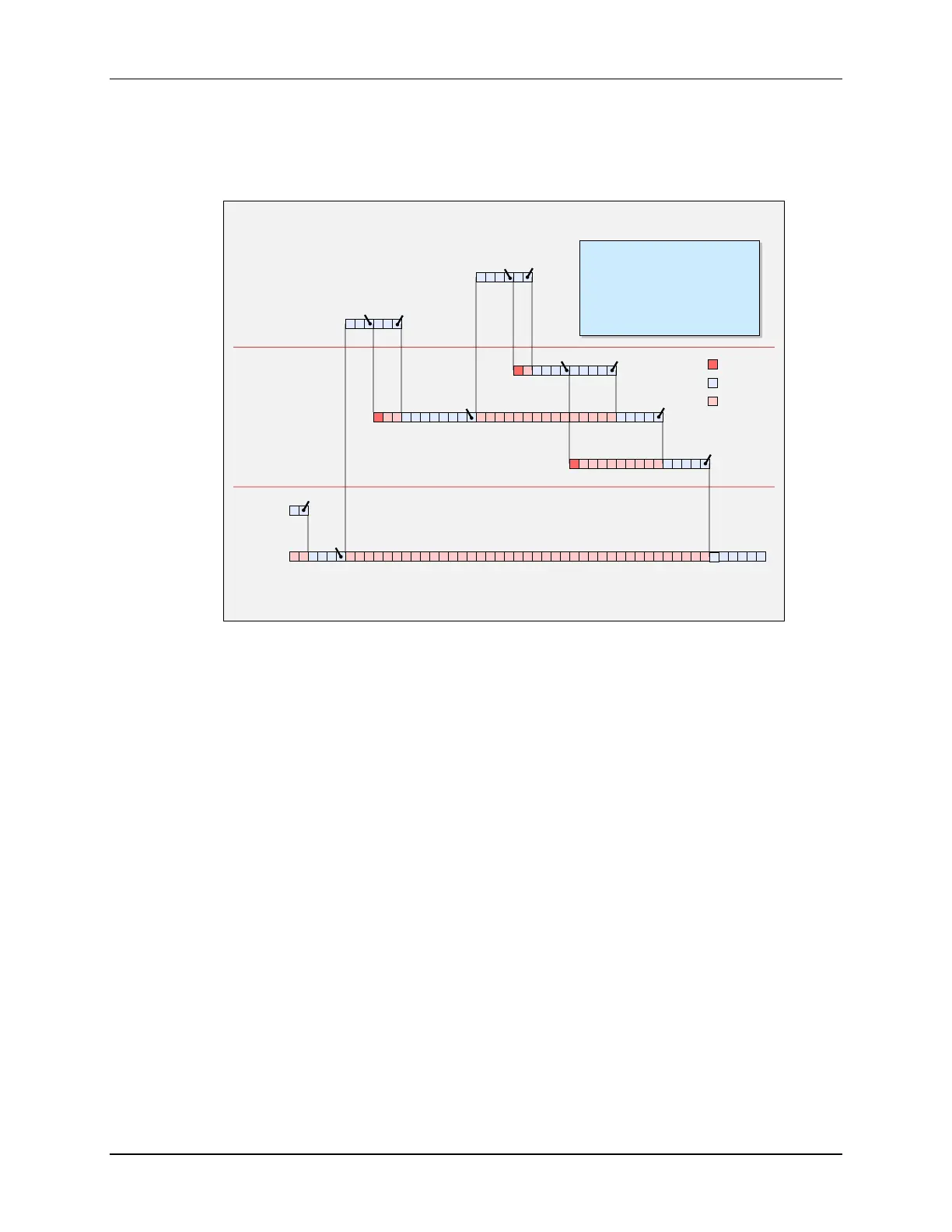

Here’s a simple, visual example of what real-time scheduling might look like in an RTOS based

system.

BIOS – Priority Based Scheduling

Hwi 2

Hwi 1

Swi 3 (Hi)

Swi 2

Swi 1 (Lo)

main

Idle

Audio_ISR()

{

read_sample();

Swi_post(Swi_2);

}

int1

start

post2 rtn

int2

post3 rtn

post1

rtn

rtn

rtn

User SETs the priorities, BIOS executes them

Posted

Running

Ready

Notice how the system enters Idle from main(). Idle is always ready to run (just as our old while{}

loop was always ready to run).

When a hardware interrupt (Hwi) occurs, we leave Idle and execute the Hwi thread’s code. Since

it appears the Hwi posted a Swi, that’s where the TI-RTOS scheduler goes to once the Hwi

finishes.

We won’t go through the remaining details in this course, though we suspect that you can all

follow the diagram. For this slide, and a lot more information, please refer to the TI-RTOS Kernel

Workshop.

MSP430 Workshop - Interrupts 5 - 35

Loading...

Loading...