MB95630H Series

510 FUJITSU SEMICONDUCTOR LIMITED MN702-00009-2v0-E

CHAPTER 24 I

2

C BUS INTERFACE

24.6 Operations and Setting Procedure Example

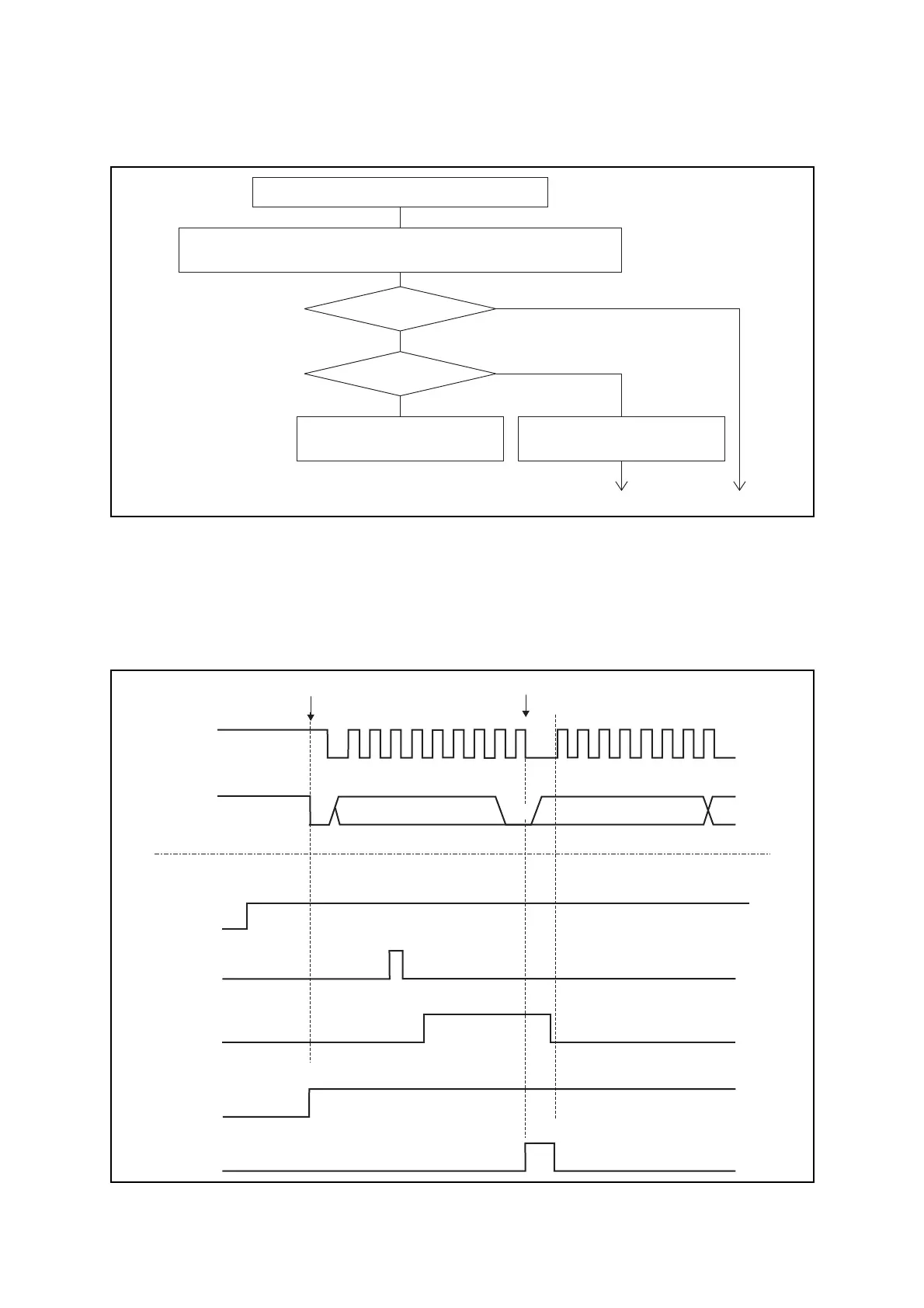

The following sample flow chart illustrates the procedure:

Figure 24.6-5 Sample Flow Chart 1

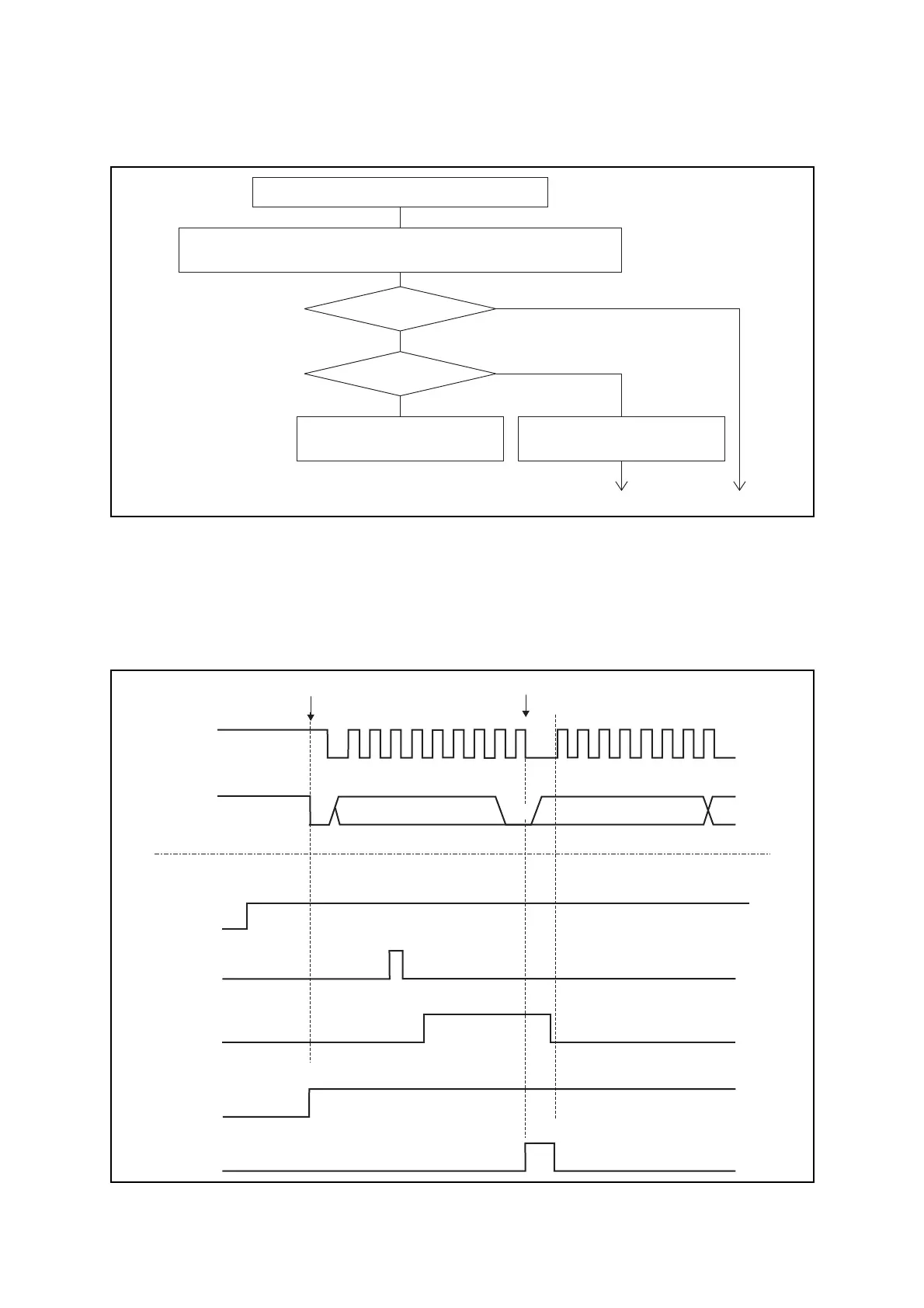

● Example of generating an interrupt (IBCR1n:INT = 1) with "IBCR0n:ALF = 1" detected

If a START condition is generated by the program (by setting the IBCR1n:MSS bit to "1")

with the bus busy (IBSRn:BB = 1) and arbitration lost detected, a IBCR1n:INT bit interrupt

occurs upon detection of "IBCR0n:ALF = 1".

Figure 24.6-6 Timing Diagram with Interrupt Generated with "IBCR0n:ALF = 1" Detected

IBCR0n:ALF = 1

IBSRn:BB = 0

YES

YES

NO

NO

Set master mode.

Set the MSS bit in I

2

C bus control register 1 ch. n (IBCR1n) to "1".

Enable AL interrupts (IBCR0n:ALE =1).

Normal control

Write "0" to IBCR0n:ALF to

clear AL flag and interrupt.

Write "0" to IBCR0n:ALE to

clear AL interrupt.

DataSlave address

START condition

Interrupt in 9th clock cycle

SCLn pin

SDAn pin

ICCRn:EN

IBCR1n:MSS

IBCR0n:ALF

IBSRn:BB

IBCR1n:INT

Clear IBCR0n:ALF by software.

Clear IBCR1n:INT by software

and release SCLn line.

ACK

Loading...

Loading...