Section 5 Power-Down Modes

Rev. 7.00 Mar 10, 2005 page 129 of 652

REJ09B0042-0700

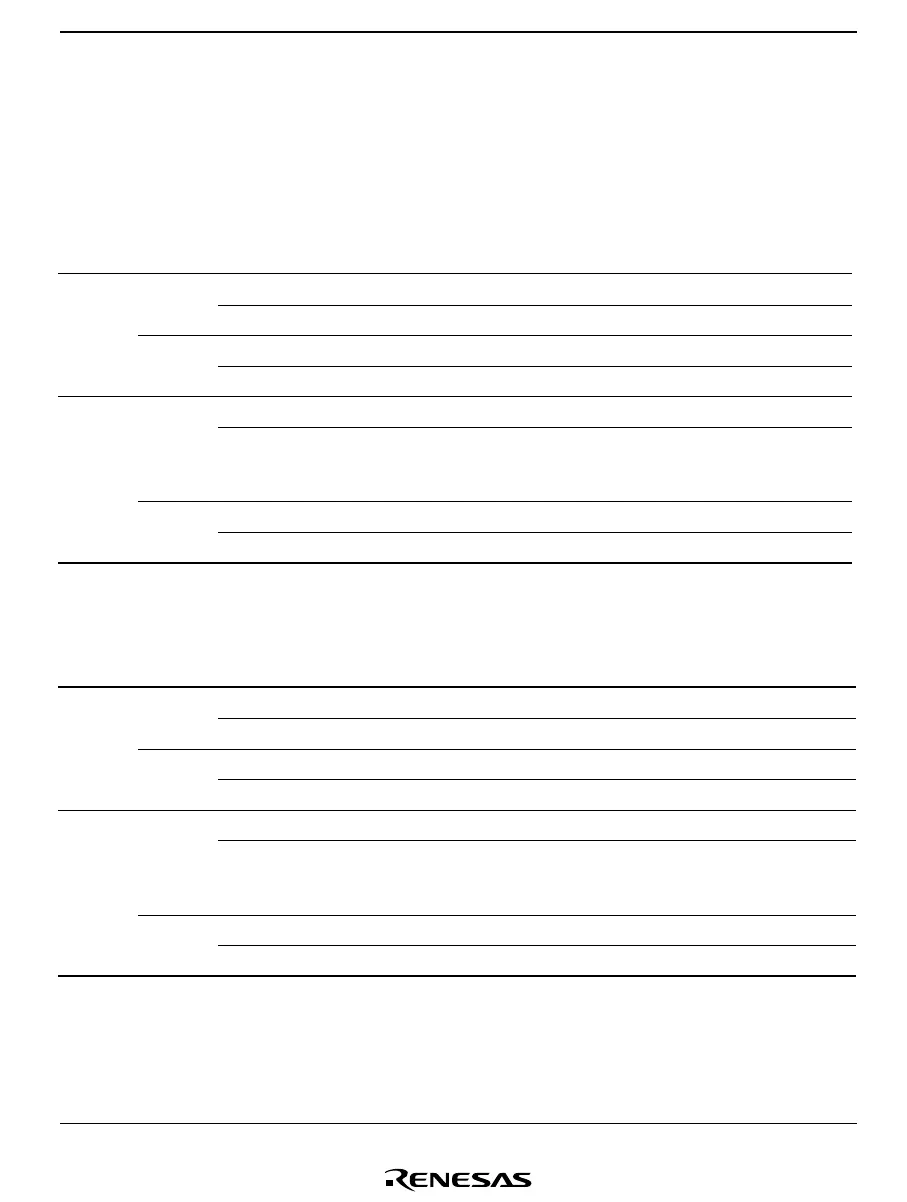

• When a oscillator is used

The table below gives settings for various operating frequencies. Set bits STS2 to STS0 for a

wait time at least as long as the oscillation stabilization time.

Table 5.4(1) Clock Frequency and Stabilization Time (H8/38024, H8/38024S,

H8/38024R Group)

(Unit: ms)

STS2 STS1 STS0 Wait Time 5 MHz 2 MHz

0 0 0 8,192 states 1.638 4.1

1 16,384 states 3.277 8.2

1 0 1,024 states 0.205 0.512

1 2,048 states 0.410 1.024

1 0 0 4,096 states 0.819 2.048

1 2 states

(Use prohibited with other than

external clock)

0.0004 0.001

1 0 8 states 0.002 0.004

1 16 states 0.003 0.008

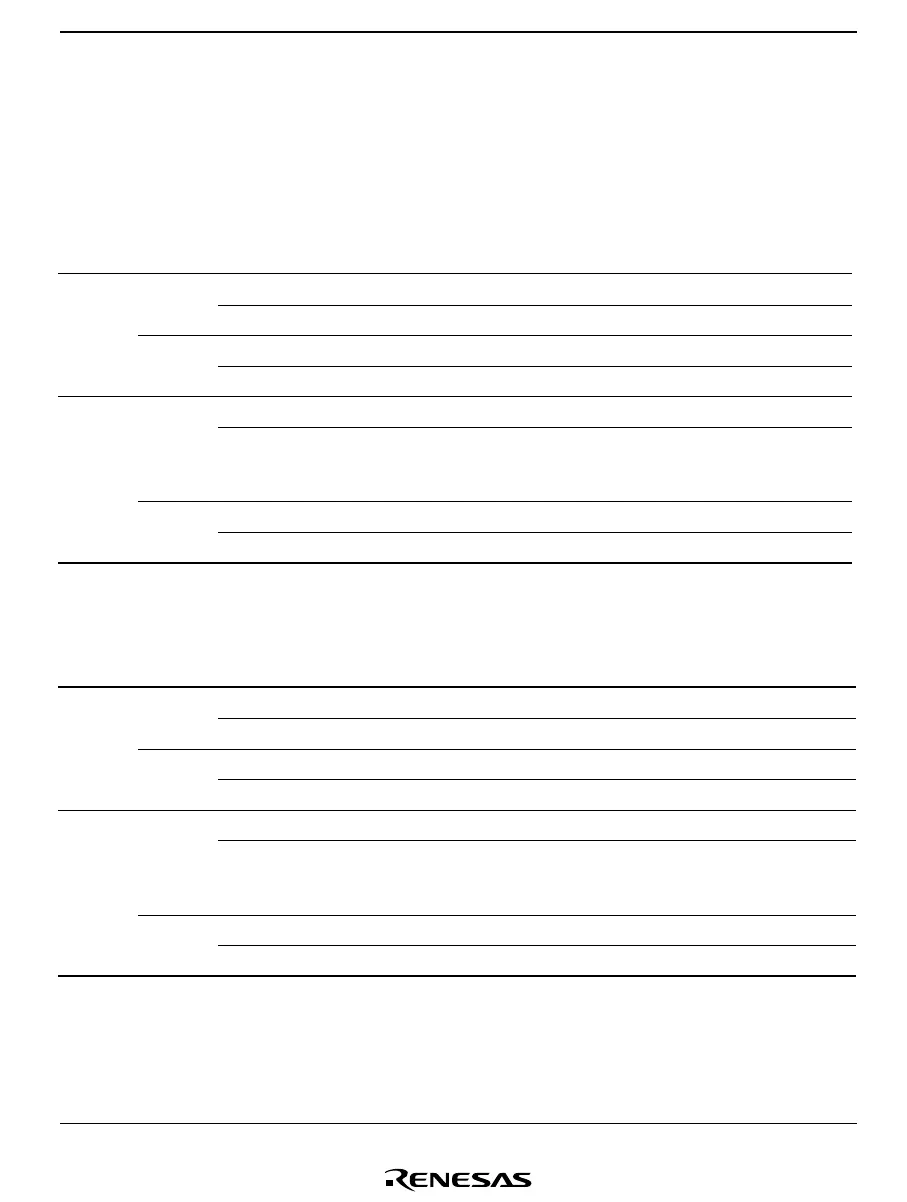

Table 5.4(2) Clock Frequency and Stabilization Time (H8/38124 Group)

(Unit: ms)

STS2 STS1 STS0 Wait Time 5 MHz 2 MHz

0 0 0 8,192 states 1.638 4.1

1 16,384 states 3.277 8.2

1 0 32,768 states 6.554 16.4

1 65,536 states 13.108 32.8

1 0 0 131,072 states 26.216 65.5

1 2 states

(Use prohibited with other than

external clock)

0.0004 0.001

1 0 8 states 0.002 0.004

1 16 states 0.003 0.008

• When an external clock is used

STS2 = 1, STS1 = 0, and STS0 = 1 should be set. Other values possible use, but CPU

sometimes will start operation before wait time completion.

Loading...

Loading...