Section 3 Exception Handling

Rev. 7.00 Mar 10, 2005 page 101 of 652

REJ09B0042-0700

executed immediately after the port mode register (or AEGSR) access without executing an

intervening instruction, the flag will not be cleared.

An alternative method is to avoid the setting of interrupt request flags when pin functions are

switched by keeping the pins at the high level so that the conditions in table 3.5 do not occur.

However, the procedure in Figure 3.7 is recommended because IECPWM is an internal signal and

determining its value is complicated.

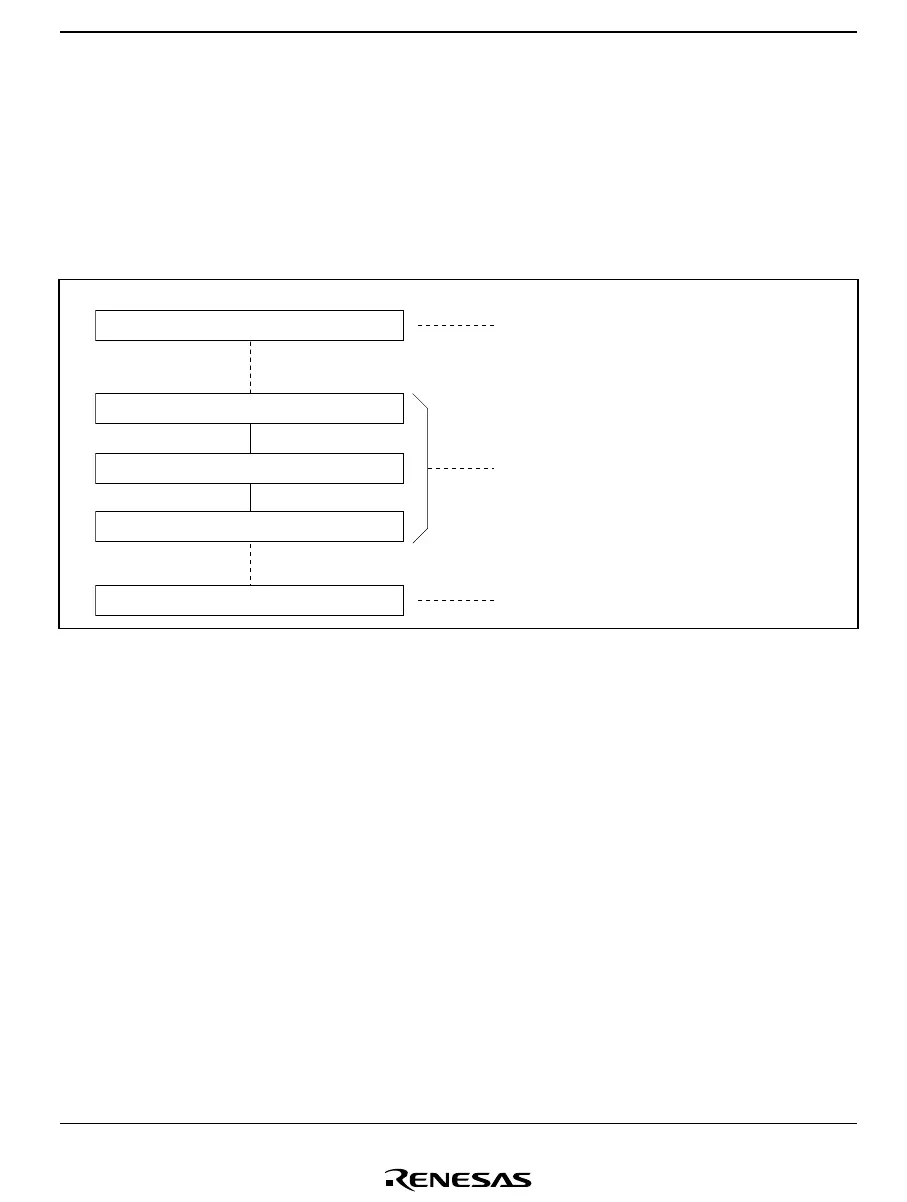

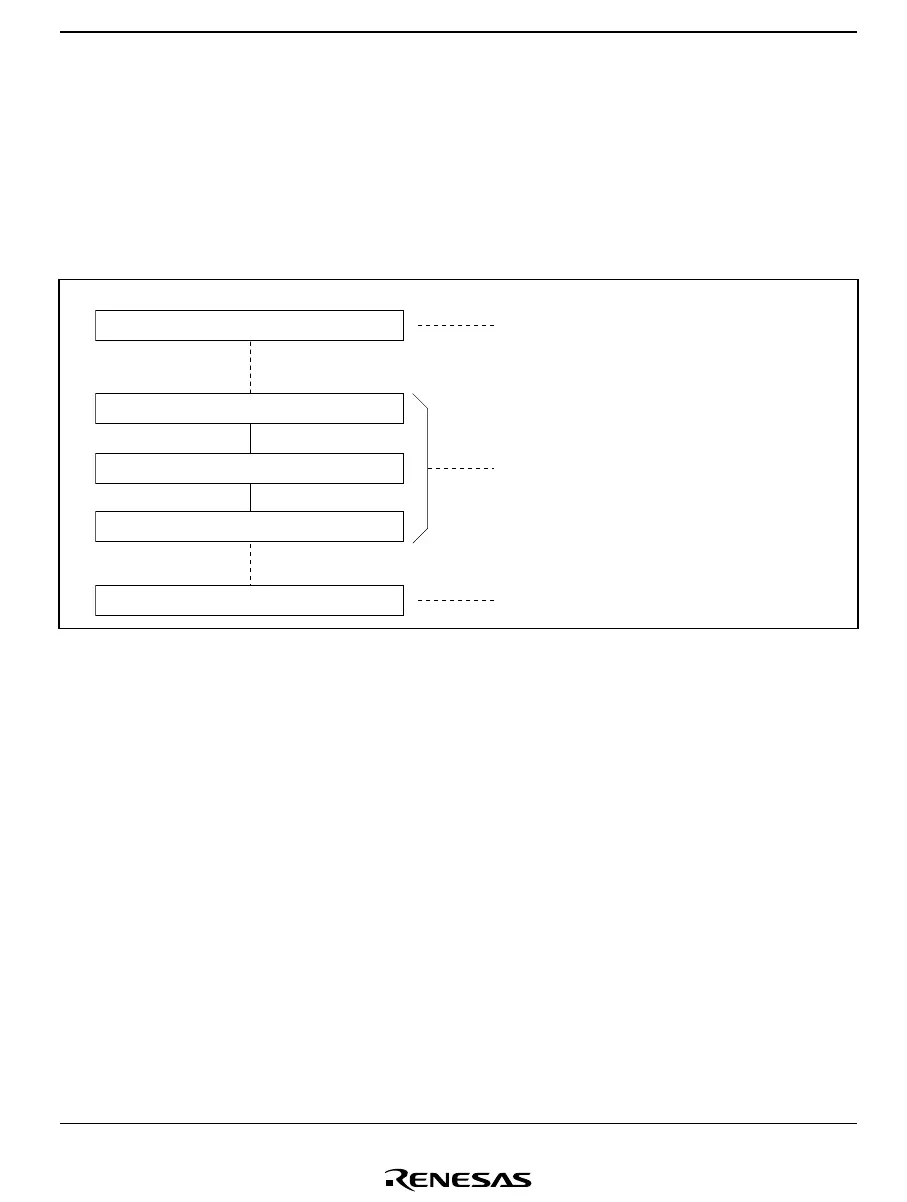

CCR I bit 1

Set port mode register (or AEGSR) bit

Execute NOP instruction

Interrupts masked. (Another possibility

is to disable the relevant interrupt in

interrupt enable register 1.)

After setting the port mode register

(or AEGSR) bit, first execute at least

one instruction (e.g., NOP), then clear

the interrupt request flag to 0

Interrupt mask cleared

Clear interrupt request flag to 0

←

CCR I bit 0

←

Figure 3.7 Port Mode Register (or AEGSR) Setting and Interrupt Request Flag

Clearing Procedure

3.4.3 Method for Clearing Interrupt Request Flags

Use the recommended method, given below when clearing the flags of interrupt request registers

(IRR1, IRR2, IWPR).

• Recommended method

Use a single instruction to clear flags. The bit control instruction and byte-size data transfer

instruction can be used. Two examples of program code for clearing IRRI1 (bit 1 of IRR1) are

given below.

BCLR #1, @IRR1:8

MOV.B R1L, @IRR1:8 (set the value of R1L to B'11111101)

Loading...

Loading...